1.本技术涉及显示技术领域,尤其涉及一种显示面板和显示装置。

背景技术:

2.目前,显示面板在出厂前通常需要对其进行屏幕检测(cell test)或称点屏检测,该部分测试用的电路称为测试电路,该测试电路能够在半成品显示面板中检测显示屏中存在的不良,减少存在不良的显示屏对显示模组资源的耗费,从而减少不必要的生产成本。半成品显示面板的显示屏由于尚未贴附偏光片,也没有焊接ic(intera ted circuit,集成电路)和fpc(flexible printed circuit board,柔性电路板),无法直接点亮。为了点亮显示屏,通常会在显示屏的绑定区将所有信号线分组连接,并将分组后的走线引出连接至测试端子(cell test pad)上,当通过外部探针给cell test pad加载合适的电学信号时,配合外置偏光片,即可点亮显示屏,以检测显示屏中存在的不良。

3.由于测试走线与各扇出走线的连接处的位置不同,导致位于外侧的扇出走线在测试时的实际阻抗小于位于内侧的扇出走线在测试时的实际阻抗,从而导致测试时出现不同区域显示亮度不同,从而分屏现象,影响测试结果。因此,本领域技术人员亟需一种解决测试时分屏现象的显示面板。

技术实现要素:

4.本技术的目的是提供一种显示面板和显示装置,以改善显示面板在测试时,出现的分屏现象影响测试效果的问题。

5.本技术公开了一种显示面板,所述显示面板包括显示区和非显示区,所述非显示区包括绑定区和布线区,所述显示面板还包括:设置在布线区的多条扇出走线、设置在所述绑定区的绑定引脚、至少两条测试总线和至少两个测试端子,所述绑定引脚一一对应连接多条扇出走线;多条所述扇出走线通过多个绑定引脚至少连接到一条所述测试总线上,所述测试端子一一对应连接所述测试总线;所述绑定区包括冗余区和两个引脚区,所述冗余区设置在两个所述引脚区之间,所述绑定引脚分别设置在所述引脚区,所述测试总线包括对应设置所述绑定区的测试走线段,所述测试走线段的延伸方向与所述扇出走线的延伸方向交叉;所述测试走线段包括对应所述引脚区设置的第一分段和对应所述冗余区设置的第二分段,所述第二分段设置在两条第一分段之间,且所述第二分段的两端分别连通两条所述第一分段;所述第二分段的电阻小于所述第一分段的电阻。

6.可选的,所述第二分段的线宽大于所述第一分段的线宽。

7.可选的,所述测试总线还包括至少两条并联测试线,所述并联测试线与所述第二分段并联设置,所述并联测试线的两端与所述第二分段的两端连接。

8.可选的,所述并联测试线设置在所述第二分段上,所述并联测试线与所述第二分段之间还设置有绝缘层,所述并联测试线的两端与所述第二分段的两端通过过孔连接。

9.可选的,当所述第二分段的线宽大于所述第一分段的线宽时,所述第二分段的两

端还设置有过渡部,所述过渡部的线宽从所述第二分段向所述第一分段的延伸方向逐渐缩小,且所述过渡部的最大线宽等于所述第二分段的线宽,所述过渡部的最小线宽等于所述第一分段的线宽。

10.可选的,所述测试总线包括测试控制线和至少一条测试信号线,所述冗余区还设置有至少一条冗余引脚,所述冗余引脚和与所述测试控制线的第二分段并联设置的并联测试线连接;所述显示面板包括第一金属层和第二金属层,所述绝缘层设置在所述第一金属层和所述第二金属层之间,所述第二分段设置在所述第一金属层,所述并联测试线设置在所述第二金属层,所述第二金属层裸露在所述绑定区。

11.可选的,所述测试总线还包括多条测试引线和多个主动开关,多个所述测试引线一一对应多个绑定引脚设置,且所述测试引线的一端连接所述绑定引脚,所述测试引线的另一端连接所述主动开关的输出端,所述主动开关的出入端连接至所述测试信号线上,所述绑定引脚通过所述测试引线连接至所述测试信号线上,所述主动开关的控制端连接所述测试控制线;所述测试端子至少设置有四个,分别设置在每条所述测试总线的两端;所述测试端子分别设置在所述绑定区的两侧;所述冗余区还设置有至少两条冗余引脚,分别与所述测试控制线对应的并联测试线和所述测试信号线对应的并联测试线连接。

12.可选的,所述冗余区的两侧至少分别设置有一条所述冗余引脚,至少一条所述并联测试线的两侧还设置有标记部,所述标记部用于与外接柔性电路板绑定时,与柔性电路板上设置的对位标记重合以实现对位。

13.可选的,在所述引脚区向所述冗余区延伸方向上,所述测试引线的长度逐渐增大,最靠近所述冗余区的所述测试引线的长度最大。

14.本技术还公开了一种显示装置,包括驱动芯片和上述的显示面板,所述驱动芯片绑定在所述显示面板的绑定区上,用于驱动所述显示面板显示。

15.本技术中,两个引脚区中最靠近冗余区的两条扇出走线在测试时实际阻抗不同,且由于测试总线对应在第二分段的长度跨越整个冗余区,因此当冗余区的长度越大时,该两条扇出走线对应的像素差异更明显,从而引发分屏现象。本技术中,通过将第二分段的电阻设置的较小,使得在测试时,两个引脚区中最靠近冗余区的两条扇出走线在测试时实际阻抗更为接近,由此实现该两条扇出走线对应的像素差异更小,在测试过程中,改善分屏现象影响测试效果的问题。

附图说明

16.所包括的附图用来提供对本技术实施例的进一步的理解,其构成了说明书的一部分,用于例示本技术的实施方式,并与文字描述一起来阐释本技术的原理。显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。在附图中:

17.图1是本技术的显示面板的示意图;

18.图2是本技术图1的放大示意图;

19.图3是本技术第二分段的截面示意图;

20.图4是本技术第二种并联测试线的示意图;

21.图5是本技术测试引线的示意图;

22.图6是本技术第二实施例的显示面板的示意图;

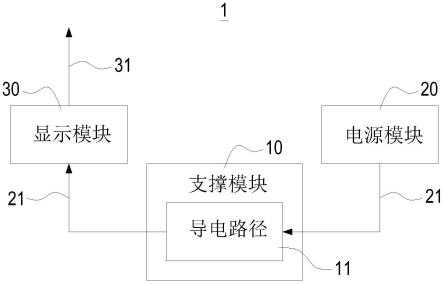

23.图7是本技术显示装置的示意图。

24.其中,1、显示装置;2、驱动芯片;10、显示面板;11、显示区;12、非显示区;13、绑定区;14、布线区;15、引脚区;16、冗余区;20、扇出走线;21、绑定引脚;22、冗余引脚;30、测试总线、31、测试端子;32、测试走线段;32a、第一分段;32b、第二分段;33、并联测试线;34、过孔;35、过渡部;36、测试控制线;37、测试信号线;38、测试引线;39、主动开关;40、标记部;50、第一金属层;51、第二金属层;52、绝缘层;

具体实施方式

25.需要理解的是,这里所使用的术语、公开的具体结构和功能细节,仅仅是为了描述具体实施例,是代表性的,但是本技术可以通过许多替换形式来具体实现,不应被解释成仅受限于这里所阐述的实施例。

26.在本技术的描述中,术语“第一”、“第二”仅用于描述目的,而不能理解为指示相对重要性,或者隐含指明所指示的技术特征的数量。由此,除非另有说明,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征;“多个”的含义是两个或两个以上。另外,“上”、“下”、“左”、“右”、“竖直”、“水平”、等指示的方位或位置关系的术语,是基于附图所示的方位或相对位置关系描述的,仅是为了便于描述本技术的简化描述,而不是指示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本技术中的具体含义。

27.下面参考附图和可选的实施例对本技术作详细说明。

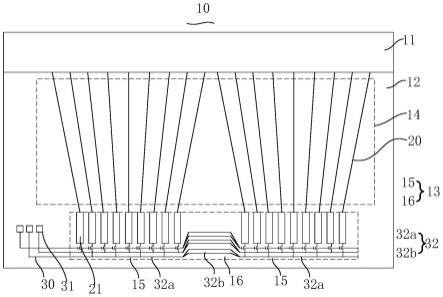

28.图1是本技术的显示面板的示意图,如图1所示,本技术公开了一种显示面板10,所述显示面板10包括显示区11和非显示区12,所述非显示区12包括绑定区13和布线区14,所述显示面板10还包括:设置在布线区14的多条扇出走线20、设置在所述绑定区13的绑定引脚21、至少两条测试总线30和至少两个测试端子31,所述绑定引脚21一一对应连接多条扇出走线20;多条所述扇出走线20通过多个绑定引脚21至少连接到一条所述测试总线30上,所述测试端子31一一对应连接所述测试总线30;所述绑定区13包括冗余区16和两个引脚区15,所述冗余区16设置在两个所述引脚区15之间,所述绑定引脚21分别设置在所述引脚区15,所述测试总线30包括对应设置所述绑定区13的测试走线段32,所述测试走线段32的延伸方向与所述扇出走线20的延伸方向交叉;所述测试走线段32包括对应所述引脚区15设置的第一分段32a和对应所述冗余区16设置的第二分段32b,所述第二分段32b设置在两条第一分段32a之间,且所述第二分段32b的两端分别连通两条所述第一分段32a;所述第二分段32b的电阻小于所述第一分段32a的电阻。

29.本技术中,两个引脚区15中最靠近冗余区16的两条扇出走线20在测试时实际阻抗不同,且由于测试总线30对应在第二分段32b的长度跨越整个冗余区16,因此当冗余区16的长度越大时,该两条扇出走线20对应的像素差异更明显,从而引发分屏现象。本技术中,通过将第二分段32b的电阻设置的较小,使得在测试时,两个引脚区15中最靠近冗余区16的两条扇出走线20在测试时实际阻抗更为接近,由此实现该两条扇出走线20对应的像素差异更小,在测试过程中,改善分屏现象影响测试效果的问题。需要说明的是,本实施例中适用的

是一种窄边框显示面板10,具体体现在,测试走线段32设置在绑定区13,且一般而言设置在绑定引脚21的下方,对应的测试端子31则设置在绑定区13的两侧,进而可以实现窄边框显示。

30.所述第二分段32b的电阻小于所述第一分段32a的电阻,其实现方案包括多种,具体方案列举如下:

31.例如,所述第二分段32b的线宽大于所述第一分段32a的线宽。本实施例中,对应冗余区16未设置扇出走线20、绑定引脚21等器件,该部分位置布线空间较大,完全可以加宽第二分段32b的宽度,由此来降低第二分段32b的电阻,该方式成本较低,影响较低,更容易实现。

32.例如,述测试总线还包括至少两条并联测试线33,所述并联测试线33与所述第二分段32b并联设置,所述并联测试线33的两端与所述第二分段32b的两端连接。本实施例中,为了降低第二分段32b的电阻,通过为第二分段32b增加并联测试线33的方式,实际上可以等同为第二分段32b增加厚度,从而降低电阻。

33.例如,增加相邻两个第二分段32b之间的间距,以减少电容串扰的问题,进而减少相邻两个第二分段32b的负载。

34.图2是本技术图1的放大示意图,如图2所示,将上述两个方案进行结合,即加宽第二分段32b的宽度,又增加并联测试线33,且并联测试线33的宽度与第二分段32b的宽度一致,使得第二分段32b的电阻尽可能降低,来平衡对应的两条扇出走线20在测试时的电阻差异。

35.具体地,当所述第二分段32b的线宽大于所述第一分段32a的线宽时,所述第二分段32b的两端还设置有过渡部35,所述过渡部35的线宽从所述第二分段32b向所述第一分段32a的延伸方向逐渐缩小,且所述过渡部35的最大线宽等于所述第二分段32b的线宽,所述过渡部35的最小线宽等于所述第一分段32a的线宽。该过渡部35尽可能避免在制程时,在第二分段32b与第一分段32a的连接处造成断裂、毛刺等问题。

36.以设置并联测试线33的方案来具体说明,所述并联测试线33设置在所述第二分段32b上,所述并联测试线33与所述第二分段32b之间还设置有绝缘层52,所述并联测试线33的两端与所述第二分段32b的两端通过过孔34连接。

37.其中,其第二分段32b一般采用金属层材料形成,而并联测试线33可以选择透明导电材料或金属材料形成。以透明导电材料来说,则并联测试线33设置在最上层,在显示面板10的膜层设置中,透明导电层一般设置在第一金属层50和第二金属层51上方。

38.图3是本技术第二分段的截面示意图。如图3所示,所述显示面板10包括第一金属层50和第二金属层51,所述绝缘层52设置在所述第一金属层50和所述第二金属层51之间,所述第二分段32b设置在所述第一金属层50,所述并联测试线33设置在所述第二金属层51,所述第二金属层51裸露在所述绑定区13。本实施例中,将并联测试线33设置在第二金属层51,并裸露在绑定区13,不设置有其它膜层覆盖并联测试线33,即类似绑定引脚21一样,裸露于绑定区13,对绑定区13的绑定引脚21具有一定的散热效果。

39.所述测试总线30包括测试控制线36和至少一条测试信号线37,所述测试总线30还包括多条测试引线38和多个主动开关39,多个所述测试引线38一一对应多个绑定引脚21设置,且所述测试引线38的一端连接所述绑定引脚21,所述测试引线38的另一端连接所述主

动开关39的输出端,所述主动开关39的出入端连接至所述测试信号线37上,所述绑定引脚21通过所述测试引线38连接至所述测试信号线37上,所述主动开关39的控制端连接所述测试控制线36。在测试时,该控制信号线为高电平时,多个主动开关39处于导通状态,数据信号由测试信号线37输出至多个扇出走线20上。在测试结束后,该控制信号线为低电平,使得多个主动开关39处于截止状态,测试引线38与测试信号线37之间断开连接,以便后续显示面板10工作时,测试信号线37不会连接对应的扇出走线20。具体地,测试信号线37一般至少包括三条,对应多列像素,一列像素分为为红色像素(r)或绿色像素(g)或蓝色像素(b),每条测试线对应一种颜色的像素连接。

40.进一步地,将并联测试线33设置在第二金属层51上,并设置为裸露的,所述测试总线30包括测试控制线36和至少一条测试信号线37,所述冗余区16还设置有至少一条冗余引脚22,所述冗余引脚22和与所述测试控制线36的第二分段32b并联设置的并联测试线33连接;该冗余引脚22通过外接的驱动芯片被驱动为低电压或接地状态,可以使得在显示面板10正常使用时,将测试控制线36的信号始终保持低电压状态。可防止该测试控制线36上掉落电荷导致将扇出走线20接通发生显示不良的情况。

41.在另一实施例中,该冗余引脚22直接与并联测试线33一次光罩成型设置,即直接使用并联测试线33的裸露部分形式冗余引脚22,该冗余引脚22可以垂直于所述绑定引脚21设计,且在与外接绑定驱动芯片时,该驱动芯片的绑定位置处同样设置对应的接地引脚与该冗余引脚22进行绑定,由于该冗余引脚22走向与其它绑定引脚21不同,该冗余引脚22还可以用作绑定中的对位标记,在外接驱动芯片例如柔性电路板(chip on film,cof)进行绑定时,该冗余引脚22可与对应柔性电路板上设置的接地引脚进行辅助对位。

42.图4是本技术第二种并联测试线的示意图,如图4所示,当然还可以进一步将冗余引脚22或并联测试线33的宽度、长度进行设计,例如,所述冗余区16的两侧至少分别设置有一条所述冗余引脚22,至少一条所述并联测试线33的两侧还设置有标记部40,所述标记部40用于与外接柔性电路板绑定时,与柔性电路板上设置的对位标记重合以实现对位。该冗余引脚22的走线与其它绑定引脚21可一致,其并联测试线33的两端可设置标记部40,如十字形、圆形、方形等标记部40。

43.在另一实施例中,还可以设置两层的并联测试线33,例如显示面板10还包括第三金属层,所述第三金属层与第二金属层51之间绝缘,且设置在第二金属层51上方,并联测试线33对应第三金属层的地方裸露,可以进一步降低第二分段32b的电阻。

44.需要理解的是,本实施例中的扇出走线20一般设置在第二金属层51,与数据线同层设置,当然为了减少布线区14的宽度,扇出走线20也可设置多层,即在第一金属层50和第二金属层51都设置扇出走线20,而绑定引脚21一般是复合结构,一般会采用双层金属层设置,来连接对应的扇出走线20。

45.进一步地,所述冗余区16还设置有至少两条冗余引脚22,分别与所述测试控制线36对应的并联测试线33和所述测试信号线37对应的并联测试线33连接。本实施例中,对应测试控制线36连接的冗余引脚22用于通过外接的驱动芯片直接提给接地或低电压,控制所有的主动开关39在正常使用时保持截止状态,而对应测试信号线37连接的冗余引脚22用于连接静电释放(esd,electro-static discharge),使得绑定区13位置的静电可通过设置的测试信号线37,以及测试信号线37对应的裸露的并联测试线33导流后释放。

46.除了上述将第二分段32b的电阻变小的方案外,图5是本技术测试引线的示意图,如图5所示,还可以对测试引线38进行改进,具体包括:在所述引脚区15向所述冗余区16延伸方向上,所述测试引线38的长度逐渐增大,最靠近所述冗余区16的所述测试引线38的长度最大。本实施例中还可以通过,在所述引脚区15向所述冗余区16延伸方向上,所述测试引线38的宽度逐渐缩小,最靠近所述冗余区16的所述测试引线38的宽度最小。以上两种方案也可以结合使用,使得从距离测试端子31最近的绑定引脚21至最远的绑定引脚21,该测试引线38的电阻逐渐降低,越靠近冗余区16,其测试引线38的电阻越低,来平衡布线导致冗余区16两侧扇出走线20的阻抗不均的问题。

47.在另一实施例中,在靠近测试端子31一侧的引脚区15中,最靠近冗余区16的绑定引脚21对应的测试引线38,该测试引线38通过主动开关39连接至第二分段32b上,且连接至第二分段32b中部偏向测试端子31的一侧,该方案也能平衡冗余区16两侧的扇出走线20的阻抗不均问题。

48.图6是本技术第二实施例的显示面板的示意图,如图6所示,本技术公开了一种显示面板10,显示面板10包括显示区11和非显示区12,所述非显示区12包括两个绑定区13和布线区14,两个绑定区13以显示面板10底边的中线对称设置,每个所述绑定区13包括两个引脚区15和一个冗余区16,显示区11内设置有多条数据线,一一对应连接布线区14的扇出走线20,且以中线将扇出走线20划分为两部分,两部分分别连接到两个引脚区15的绑定引脚21上;所述测试总线30设置有多条,其中包括测试控制线36和至少两条测试信号线37,测试总线30的延伸方向与底边大致平行,大致平行的意思是测试总线30的整体走线延伸方向与底边平行,但是存在绕线、避让等走线段,该部分走线段并不是完全与底边平行的,甚至会出现垂直于底边的情况,但是在两个绑定区13的测试走线段32,以及两个绑定区13之间的测试走线段32分别都是平行于显示面板10的底边,且垂直于绑定引脚21。所述测试走线段32包括对应所述引脚区15设置的第一分段32a和对应所述冗余区16设置的第二分段32b,所述第二分段32b设置在两条第一分段32a之间,且所述第二分段32b的两端分别连通两条所述第一分段32a;所述第二分段32b的电阻小于所述第一分段32a的电阻。具体第二分段32b的电阻小于所述第一分段32a的电阻的方案可结合上述,在此不进行赘述。该实施例中,两个绑定区13中对应冗余区16的第二分段32b都采用电阻变小的方案,可实现在测试过程中,改善冗余区16两份分屏现象影响测试效果的问题。

49.在本实施例中,对应两个绑定区13之间的测试走线段32也可以采用上述将电阻变小的方案,但是该两个绑定区13之间的测试走线段32的长度明显是大于同一个绑定区13中冗余区16的长度。因此,对应两个绑定区13中最靠近中线的两条扇出走线20而言,该两个扇出走线20对应的像素是相邻像素,但是在测试时,两条扇出走线20的电阻差异多出该两个绑定区13之间的测试走线段32的长度,因此会造成更明显的分屏问题,因此在本方案中:所述测试端子31至少设置有四个,分别设置在每条所述测试总线30的两端;所述测试端子31分别设置在两个所述绑定区13的外侧;即一侧的测试端子31从左边向左边的绑定区13对应的扇出走线20输入信号,另一侧的测试端子31从右边向右边的绑定区13对应的扇出走线20输入信号。

50.图7是本技术显示装置的示意图,如图7所示,本技术公开了一种显示装置1,包括上述任意一实施例的显示面板10和驱动芯片2,所述驱动芯片2绑定在所述显示面板10的绑

定区上,用于驱动所述显示面板显示。其显示面板适用于各种显示面板,如tn(twisted nematic,扭曲向列型)显示面板、ips(in-plane switching,平面转换型)显示面板、va(vertical alignment,垂直配向型)显示面板、mva(multi-domain vertical alignment,多象限垂直配向型)显示面板,当然,也可以是其他类型的显示面板,如oled(organic light-emitting diode,有机发光二极管)显示面板,均可适用上述方案。

51.需要说明的是,本技术的发明构思可以形成非常多的实施例,但是申请文件的篇幅有限,无法一一列出,因而,在不相冲突的前提下,以上描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例,各实施例或技术特征组合之后,将会增强原有的技术效果。

52.以上内容是结合具体的可选实施方式对本技术所作的进一步详细说明,不能认定本技术的具体实施只局限于这些说明。对于本技术所属技术领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本技术的保护范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。