1.本发明涉及一种显示装置,详细而言涉及一种显示质量得到改善的显示装置。

背景技术:

2.为了提供图像信息,正在使用各种形式的显示装置。尤其,作为显示装置,正在使用有机发光显示(organic light emitting display,oled)装置、无机发光显示(inorganic light emitting display)装置、液晶显示(liquid crystal display,lcd)装置、等离子体(plasma)显示装置等。

3.显示装置包括显示图像的显示面板以及与显示面板结合而向显示面板提供驱动信号的面板驱动块。显示面板包括产生光的像素。在发光型显示装置的情况下,包括产生光的发光二极管。

4.显示装置也可以具备能够感测从外部施加的输入的输入感测层。

技术实现要素:

5.本发明的目的在于提供一种通过防止显示装置的亮度失真来改善图像质量的显示装置。

6.根据本发明的一实施例的显示装置包括:显示面板,包括显示图像的多个像素以及分别电连接到所述像素的多个数据线。所述显示装置包括:面板驱动块,从外部接收图像信号而通过所述数据线向所述显示面板发送数据信号。所述显示面板包括:多个阻抗控制部,分别电连接到所述数据线,并响应于阻抗控制信号而调节所述数据线的每一个的阻抗。

7.作为本发明的一实施例,可以是,所述阻抗控制信号根据所述数据信号施加到所述像素的定时控制所述阻抗控制部。

8.作为本发明的一实施例,所述阻抗控制信号包括第一控制信号。所述阻抗控制部的每一个包括:第一控制晶体管,响应于所述第一控制信号,并连接到所述数据线中的相对应的数据线;以及电阻部,与所述第一控制晶体管并联连接。

9.作为本发明的一实施例,所述第一控制晶体管的第一电极与所述电阻部的第一端电连接,所述第一控制晶体管的第二电极与所述电阻部的第二端电连接。所述第一控制晶体管的控制电极与接收所述第一控制信号的第一阻抗控制线电连接。所述第一控制晶体管在所述第一控制信号的第一控制时段中截止,并在所述第一控制信号的第一非控制时段中导通。

10.作为本发明的一实施例,所述阻抗控制部在所述第一控制时段中具有第一阻抗,并在所述第一非控制时段中具有小于所述第一阻抗的第二阻抗。

11.作为本发明的一实施例,所述电阻部包括:主电阻,接通在所述第一控制晶体管的所述第一电极和所述第一控制晶体管的所述第二电极之间。

12.作为本发明的一实施例,所述电阻部还包括:多个电阻调节部,接通在所述第一控制晶体管的所述第一电极和所述第一控制晶体管的所述第二电极之间。所述电阻调节部的

每一个包括:子电阻,接通在所述第一控制晶体管的所述第一电极和所述第一控制晶体管的所述第二电极之间;以及子晶体管,接通在所述第一控制晶体管的所述第二电极和所述子电阻之间。

13.作为本发明的一实施例,所述子晶体管的控制电极与接收电阻控制信号的电阻控制线电连接。

14.作为本发明的一实施例,所述阻抗控制信号还包括第二控制信号。所述阻抗控制部的每一个包括:第二控制晶体管,响应于所述第二控制信号,并并联连接到所述相对应的数据线;以及电容器,连接到所述第二控制晶体管。所述第二控制晶体管的第一电极电连接到所述相对应的数据线,所述第二控制晶体管的第二电极与所述电容器电连接。

15.作为本发明的一实施例,所述第二控制晶体管的控制电极与接收所述第二控制信号的第二阻抗控制线电连接。所述第二控制晶体管在所述第二控制信号的第二控制时段中导通,并在所述第二控制信号的第二非控制时段中截止。

16.作为本发明的一实施例,在所述第一控制时段和所述第二控制时段重叠的重叠时段中所述数据线的每一个与所述电阻部以及所述电容器电连接。

17.作为本发明的一实施例,所述阻抗控制部的每一个包括:第二控制晶体管,响应于所述第一控制信号,并并联连接到所述相对应的数据线;以及电容器,连接到所述第二控制晶体管。所述第二控制晶体管的第一电极电连接到所述相对应的数据线,所述第二控制晶体管的第二电极与所述电容器电连接。

18.作为本发明的一实施例,所述第二控制晶体管的控制电极与所述第一阻抗控制线电连接。所述第二控制晶体管在所述第一控制信号的所述第一控制时段中导通,并在所述第一控制信号的所述第一非控制时段中截止。

19.作为本发明的一实施例,在所述第一控制时段中,所述数据线的每一个与所述电阻部以及所述电容器电连接。

20.作为本发明的一实施例,所述阻抗控制部的每一个包括:控制晶体管,响应于所述阻抗控制信号,并连接到所述数据线中的相对应的数据线;以及电容器,与所述控制晶体管连接。所述控制晶体管的第一电极电连接到所述数据线,所述控制晶体管的第二电极与所述电容器电连接。

21.作为本发明的一实施例,所述控制晶体管的控制电极与接收所述阻抗控制信号的阻抗控制线电连接。所述控制晶体管在所述阻抗控制信号的控制时段中导通,并在所述阻抗控制信号的非控制时段中截止。

22.作为本发明的一实施例,所述阻抗控制部在所述控制时段中具有第一阻抗,并在所述非控制时段中具有小于所述第一阻抗的第二阻抗。

23.作为本发明的一实施例,所述显示面板包括配置所述像素的显示区域以及与所述显示区域相邻的非显示区域。可以是,所述阻抗控制部配置在所述非显示区域中。

24.作为本发明的一实施例,所述面板驱动块包括:控制器,生成源极控制信号以及栅极控制信号,并基于所述图像信号生成图像数据。所述面板驱动块包括:源极驱动块,从所述控制器接收所述源极控制信号以及所述图像数据,并基于所述图像数据生成所述数据信号。可以是,所述阻抗控制部配置在所述源极驱动块和所述像素之间。

25.作为本发明的一实施例,所述显示面板还包括:多个扫描线,分别电连接到所述像

素。所述面板驱动块还包括:栅极驱动块,将基于所述栅极控制信号生成的扫描信号通过所述扫描线依次发送给所述显示面板。所述栅极驱动块将所述阻抗控制信号发送给所述阻抗控制部。

26.作为本发明的一实施例,所述阻抗控制部在所述阻抗控制信号的控制时段中具有第一阻抗,并在所述阻抗控制信号的非控制时段中具有小于所述第一阻抗的第二阻抗。可以是,所述控制时段与扫描时段重叠。

27.作为本发明的一实施例,可以是,所述扫描时段包括在所述控制时段中。

28.作为本发明的一实施例,可以是,所述显示面板包括:基底层;电路元件层,配置在所述基底层上,并包括用于驱动发光元件的多个驱动晶体管;以及显示元件层,配置在所述电路元件层上,并包括所述发光元件。所述阻抗控制部的每一个包括:阻抗部;以及控制晶体管,控制所述阻抗部。可以是,所述阻抗部以及所述控制晶体管配置在所述电路元件层中。

29.作为本发明的一实施例,可以是,所述阻抗部配置在与所述驱动晶体管中的至少一个驱动晶体管的半导体图案相同的层上。

30.作为本发明的一实施例,可以是,所述阻抗部包括多晶硅。

31.作为本发明的一实施例,可以是,所述阻抗部包括金属氧化物。

32.根据本发明的一实施例的显示装置包括:显示面板,包括显示图像的多个像素以及分别电连接到所述像素的多个数据线。所述显示装置包括:输入感测层,配置在所述显示面板上,并感应从外部施加的输入;以及面板驱动块,从外部接收图像信号而通过所述数据线向所述显示面板发送数据信号。所述显示面板包括:多个阻抗控制部,分别电连接到所述数据线,并响应于阻抗控制信号而调节所述数据线的每一个的阻抗。

33.作为本发明的一实施例,所述显示面板包括:显示元件层,包括发光元件;以及封装层,配置在所述显示元件层上。

34.作为本发明的一实施例,可以是,所述输入感测层直接配置在所述封装层上。

35.作为本发明的一实施例,所述显示面板包括配置所述像素的显示区域以及与所述显示区域相邻的非显示区域。可以是,所述阻抗控制部配置在所述非显示区域中。

36.作为本发明的一实施例,所述面板驱动块包括:控制器,生成源极控制信号以及栅极控制信号,并基于所述图像信号生成图像数据。所述面板驱动块包括:源极驱动块,从所述控制器接收所述源极控制信号以及所述图像数据,并基于所述图像数据生成所述数据信号。可以是,所述阻抗控制部配置在所述源极驱动块和所述像素之间。

37.作为本发明的一实施例,所述显示面板还包括:多个扫描线,分别电连接到所述像素。所述面板驱动块还包括:栅极驱动块,将基于所述栅极控制信号生成的扫描信号通过所述扫描线依次发送给所述显示面板。在所述扫描信号的扫描时段中,所述数据信号施加到所述像素。

38.根据本发明,可以通过控制数据线的阻抗来防止从外部输入到显示装置的外部输入引起的像素的亮度失真。

附图说明

39.图1是根据本发明的一实施例的显示装置的立体图。

40.图2是图1所示的显示装置的分解立体图。

41.图3是图2所示的显示模组的截面图。

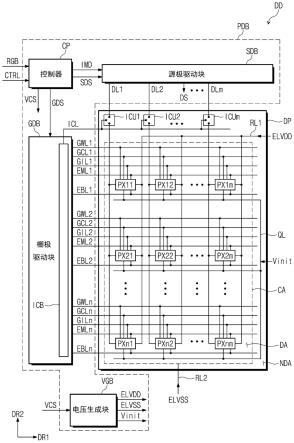

42.图4是根据本发明的一实施例的显示装置的框图。

43.图5是根据本发明的一实施例的显示模组的一部分区域中的截面图。

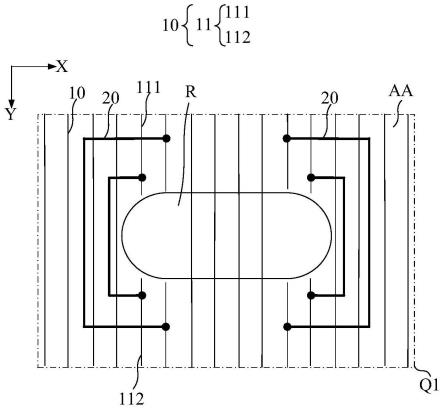

44.图6是示出根据本发明的一实施例的输入感测层的构成的平面图。

45.图7是根据本发明的一实施例的像素的电路图。

46.图8是用于驱动图7所示的像素的驱动信号的波形图。

47.图9是用于说明根据本发明的一实施例的阻抗控制部的工作的驱动信号的波形图。

48.图10a至图10c是用于说明包括电阻部的阻抗控制部的结构的电路图。

49.图11以及图12是用于说明包括电阻部以及电容器的阻抗控制部的结构的电路图。

50.图13是用于说明包括电容器的阻抗控制部的结构的电路图。

具体实施方式

51.在本说明书中,当提及某构成要件(或区域、层、部分等)“在”另外构成要件“上”、“连接于”或“结合于”另外构成要件时,意指某构成要件可以直接配置/连接/结合在另外构成要件上,或者也可以在它们之间配置有第三构成要件。

52.相同的附图标记指代相同的构成要件。另外,在附图中,构成要件的厚度、比例及尺寸是为了技术内容的有效说明而放大的。“和/或”将关联的构成要件所能定义的一个以上的组合全部包括。

53.第一、第二等术语可用于说明各种构成要件,但所述构成要件并不被所述术语所限制。所述术语仅用于将一个构成要件与另外构成要件区分的目的。例如,在不脱离本发明的权利范围的情况下,第一构成要件可命名为第二构成要件,类似地,第二构成要件也可命名为第一构成要件。只要在文脉上没有明确表示为不同,单数表达包括复数表达。

54.另外,“下方”、“下侧”、“上方”、“上侧”等术语用于说明附图中示出的构成要件的关联关系。所述术语是相对性概念,以附图中表示的方向为基准进行说明。

[0055]“包括”或“具有”等术语应理解为用于指定说明书中所记载的特征、数字、步骤、工作、构成要件、部件或它们的组合的存在,并不是预先排除一个或其以上的其它特征,或者数字、步骤、工作、构成要件、部件或它们的组合的存在或附加可能性。

[0056]

只要没有不同地定义,本说明书中使用的所有术语(包括技术术语及科学术语)具有与本发明所属技术领域的技术人员通常所理解的含义相同的含义。另外,通常使用的词典中所定义的术语之类的术语应解释为具有与相关技术的脉络上所具有的含义相同的含义,只要没有明确地在此定义,不应被解释为过于理想化或过于形式化的含义。

[0057]

以下,参照附图说明本发明的实施例。

[0058]

图1是根据本发明的一实施例的显示装置的立体图,图2是图1所示的显示装置的分解立体图。

[0059]

参照图1以及图2,显示装置dd可以是根据电信号激活的装置。根据本发明的显示装置dd可以是包括电视机、监视器等之类的大型显示装置,以及便携电话、平板、汽车导航仪、游戏机等之类中小型显示装置。这些仅作为实施例提出,显然,只要不脱离本发明的概

念,也可以用于其它电子设备。

[0060]

显示装置dd具有长方形形状,所述长方形形状在第一方向dr1上具有长边并在与第一方向dr1交叉的第二方向dr2上具有短边。但是,显示装置dd的形状不限于此,可以提供各种形状的显示装置dd。显示装置dd可以在与第一方向dr1以及第二方向dr2的每一个平行的显示面is中朝向第三方向dr3显示图像im。显示图像im的显示面is可以与显示装置dd的正面(front surface)相对应。

[0061]

在本实施例中,以显示图像im的方向为基准定义各部件的正面(或者上面)和背面(或者下面)。可以是,正面和背面在第三方向dr3上彼此相对(opposing),正面和背面的每一个的法线方向与第三方向dr3平行。

[0062]

在第三方向dr3上的正面和背面之间的隔开距离可以与显示装置dd在第三方向dr3上的厚度相对应。另一方面,第一至第三方向dr1、dr2、dr3所指示的方向是相对性概念,可以转换为其它方向。

[0063]

显示装置dd可以感测从外部施加的外部输入。外部输入可以包括从显示装置dd的外部提供的各种形式的输入。根据本发明的一实施例的显示装置dd可以感测从外部施加的用户us的外部输入tc。用户us的外部输入tc可以是用户身体的一部分、光、热或者压力等各种形式的外部输入中的任意一个或者它们的组合。在本实施例中,以用户us的外部输入tc是施加到正面的由用户us的手引起的触摸输入为例进行说明,但其是示例性的,如上所述,用户us的外部输入tc可以提供为各种形式。另外,显示装置dd也可以根据显示装置dd的结构感测施加到显示装置dd的侧面或背面的用户us的外部输入tc,不限于任何一个实施例。

[0064]

显示装置dd的正面可以划分为透射区域ta以及边框区域bza。透射区域ta可以是显示图像im的区域。用户通过透射区域ta识别图像im。在本实施例中,透射区域ta以顶点为圆的矩形形状示出。然而,其是示例性示出的,透射区域ta可以具有各种形状,不限于任何一个实施例。

[0065]

边框区域bza与透射区域ta相邻。边框区域bza可以具有预定的颜色。边框区域bza可以围绕透射区域ta。由此,透射区域ta的形状可以实质上由边框区域bza界定。然而,其是示例性示出的,边框区域bza也可以配置为仅与透射区域ta的一侧相邻,也可以省略。根据本发明的一实施例的显示装置dd可以包括各种实施例,不限于任何一个实施例。

[0066]

如图2所示,显示装置dd可以包括显示模组dm以及配置在显示模组dm上的窗口wm。显示模组dm可以包括根据电信号显示图像的显示面板dp以及发送/接收针对外部输入的信息的输入感测层isp。

[0067]

根据本发明的一实施例的显示面板dp可以是发光型显示面板。作为其一例,显示面板dp可以是有机发光显示面板、无机发光显示面板或者量子点(quantum dot)发光显示面板。有机发光显示面板的发光层可以包括有机发光物质。无机发光显示面板的发光层可以包括无机发光物质。量子点发光显示面板的发光层可以包括量子点以及量子棒等。以下,在本实施例中,显示面板dp说明为有机发光显示面板。

[0068]

可以是,显示面板dp输出图像im,输出的图像im通过显示面is显示。

[0069]

输入感测层isp可以配置在显示面板dp上而感测外部输入tc。将在下面参照图5以及图6叙述输入感测层isp的构成以及工作。

[0070]

窗口wm可以由能够射出图像im的透明的物质形成。例如,可以由玻璃、蓝宝石、塑

料等构成。窗口wm示出为单层,但不限于此,可以包括多个层。

[0071]

另一方面,虽然未示出,但是上述的显示装置dd的边框区域bza可以实质上提供为在窗口wm的一区域中印刷有包括预定的颜色的物质的区域。作为本发明的一例,窗口wm可以包括用于定义边框区域bza的遮光图案。遮光图案作为有色的有机膜,例如,可以通过涂层方式形成。

[0072]

窗口wm可以通过粘合膜结合到显示模组dm。作为本发明的一例,粘合膜可以包括光学透明粘合膜(oca,optically clear adhesive film)。但是,粘合膜不限于此,可以包括常规的粘合剂或者粘着剂。例如,粘合膜可以包括光学透明粘合树脂(ocr,optically clear resin)或者压敏粘合膜(psa,pressure sensitive adhesive film)。

[0073]

在窗口wm和显示模组dm之间可以还配置防反射层。防反射层减少从窗口wm的上侧入射的外部光的反射率。根据本发明的一实施例的防反射层可以包括相位延迟器(retarder)以及偏振器(polarizer)。相位延迟器可以是膜类型或者液晶涂层类型,可以包括λ/2相位延迟器和/或λ/4相位延迟器。偏振器也可以是膜类型或者液晶涂层类型。可以是,膜类型包括拉伸型合成树脂膜,液晶涂层类型包括排列为预定的排列的液晶。相位延迟器以及偏振器可以实现为一个偏振膜。

[0074]

作为本发明的一例,防反射层也可以包括滤色器。可以考虑包括在显示面板dp中的多个像素px11~pxnm(参照图4)所生成的光的颜色来确定滤色器的排列。防反射层也可以还包括遮光图案。

[0075]

显示面板dp可以定义为显示区域da以及非显示区域nda。显示区域da可以定义为射出从显示面板dp提供的图像的区域。另外,显示区域da也可以定义为输入感测层isp感测从外部施加的外部输入tc的区域。

[0076]

非显示区域nda与显示区域da相邻。例如,非显示区域nda可以围绕显示区域da。然而,其是示例性示出的,非显示区域nda可以定义为各种形状,不限于任何一个实施例。根据一实施例,显示面板dp的显示区域da可以与透射区域ta的至少一部分相对应。

[0077]

显示模组dm可以还包括主电路基板mcb、柔性电路膜fcb以及驱动芯片dic。主电路基板mcb可以与柔性电路膜fcb接通而与显示面板dp电连接。柔性电路膜fcb接通到显示面板dp而电连接显示面板dp和主电路基板mcb。

[0078]

主电路基板mcb可以包括多个驱动元件。多个驱动元件可以包括用于驱动显示面板dp的电路部。在柔性电路膜fcb上可以装配驱动芯片dic。根据本发明的一实施例的柔性电路膜fcb示出为一个,但不限于此,可以提供为多个而接通到显示面板dp。图2中示出了驱动芯片dic装配在柔性电路膜fcb上的结构,但本发明不限于此。例如,驱动芯片dic可以直接装配在显示面板dp上。在此情况下,显示面板dp的装配有驱动芯片dic的部分可以弯曲而配置在显示模组dm的背面。另外,驱动芯片dic也可以直接装配在主电路基板mcb上。

[0079]

输入感测层isp可以通过柔性电路膜fcb与主电路基板mcb电连接。但是,本发明的实施例不限于此。即,显示模组dm可以追加包括用于将输入感测层isp电连接到主电路基板mcb的单独的柔性电路膜。

[0080]

显示装置dd还包括容纳显示模组dm的外部壳体edc。外部壳体edc可以与窗口wm结合而定义显示装置dd的外观。外部壳体edc通过吸收从外部施加的冲击并防止异物/水分等渗透到显示模组dm来保护容纳在外部壳体edc中的构成。另一方面,作为本发明的一例,外

部壳体edc可以提供为多个收纳部件结合的形式。

[0081]

根据一实施例的显示装置dd可以还包括包括用于使显示模组dm工作的各种功能性模组的电子模组、供应显示装置dd的整体工作所需的电源的电源供应模组、与显示模组dm和/或外部壳体edc结合而分割显示装置dd的内部空间的支架等。

[0082]

图3是图2所示的显示模组的截面图。

[0083]

参照图3,显示模组dm包括显示面板dp和输入感测层isp。显示面板dp包括基底层bl、配置在基底层bl上的电路元件层dp-cl、显示元件层dp-oled以及封装层tfe。虽然没有单独示出,但是显示面板dp可以还包括防反射层、折射率调节层等之类功能层。

[0084]

基底层bl可以包括至少一个塑料膜。基底层bl可以包括塑料基板、玻璃基板、金属基板或者有机/无机复合材料基板等。作为本发明的一例,基底层bl可以是柔性的基板。参照图2说明的显示区域da和非显示区域nda可以在基底层bl中相同地定义。

[0085]

电路元件层dp-cl包括至少一个中间绝缘层和电路元件。中间绝缘层包括至少一个中间无机层和至少一个中间有机层。所述电路元件包括信号线、像素的驱动电路等。

[0086]

显示元件层dp-oled包括发光元件。发光元件可以包括有机发光二极管。显示元件层dp-oled可以还包括像素界定膜之类有机膜。

[0087]

封装层tfe密封显示元件层dp-oled。封装层tfe包括至少一个无机层。封装层tfe可以还包括至少一个有机层。无机层保护显示元件层dp-oled免受水分/氧气的影响,有机层保护显示元件层dp-oled免受灰尘颗粒之类异物的影响。无机层可以包括硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或者铝氧化物层等。有机层可以包括丙烯酸系列有机层,但不限于此。

[0088]

然而,作为本发明的一例,显示面板dp也可以还包括封装基板。封装基板可以配置为在显示元件层dp-oled上与基底层bl面对。封装基板可以包括塑料基板、玻璃基板、金属基板或者有机/无机复合材料基板等。可以是,在封装基板和基底层bl之间配置密封剂,封装基板和基底层bl通过密封剂彼此结合。密封剂也可以包括有机粘合剂或者陶瓷粘合材料即玻璃胶(frit)等。显示元件层dp-oled可以通过密封剂以及封装基板密封。

[0089]

输入感测层isp可以通过连续工艺形成在显示面板dp上。另外,输入感测层isp和显示面板dp可以通过粘合膜彼此结合。输入感测层isp可以具有多层结构。输入感测层isp可以包括单层或者多层的绝缘层。根据本发明的一实施例,当输入感测层isp通过连续工艺直接配置在显示面板dp上时,输入感测层isp直接配置在封装层tfe上,粘合膜不配置在输入感测层isp和显示面板dp之间。但是,作为另一例,在输入感测层isp和显示面板dp之间可以配置粘合膜。在此情况下,可以是,输入感测层isp不是通过与显示面板dp连续的工艺制造,而是通过相对于显示面板dp独立的工艺制造之后,通过粘合膜固定到显示面板dp的上面。

[0090]

当输入感测层isp通过连续工艺直接配置在显示面板dp上时,输入感测层isp可以直接配置在封装基板上。但是,作为另一例,当输入感测层isp和显示面板dp之间配置粘合膜时,输入感测层isp可以通过粘合膜固定到封装基板的上面。

[0091]

图4是根据本发明的一实施例的显示装置的框图。

[0092]

参照图4,显示装置dd包括显示面板dp以及面板驱动块pdb。

[0093]

作为本发明的一例,面板驱动块pdb包括控制器cp、源极驱动块sdb、栅极驱动块

gdb以及电压生成块vgb。

[0094]

控制器cp从外部接收图像信号rgb以及外部控制信号ctrl。控制器cp转换图像信号rgb的数据格式以与和源极驱动块sdb的接口(interface)规格相匹配,并生成图像数据imd。控制器cp基于图像信号rgb以及外部控制信号ctrl生成源极控制信号sds、栅极控制信号gds以及电压控制信号vcs。外部控制信号ctrl可以包括垂直同步信号、水平同步信号以及主时钟等。

[0095]

控制器cp可以将图像数据imd以及源极控制信号sds发送给源极驱动块sdb。源极控制信号sds可以包括启动源极驱动块sdb的工作的水平起始信号。源极驱动块sdb响应于源极控制信号sds而基于图像数据imd生成数据信号ds。源极驱动块sdb将数据信号ds输出到将在下面叙述的多个数据线dl1~dlm。数据信号ds是与图像数据imd的灰度值相对应的模拟电压。

[0096]

栅极驱动块gdb从控制器cp接收栅极控制信号gds。栅极控制信号gds可以包括启动栅极驱动块gdb的工作的垂直起始信号、确定信号的输出时机的时钟信号等。栅极驱动块gdb基于栅极控制信号gds生成多个扫描信号、多个补偿扫描信号以及多个初始化扫描信号。栅极驱动块gdb将扫描信号依次输出到多个扫描线gwl1~gwln,将补偿扫描信号依次输出到多个补偿线gcl1~gcln,将初始化扫描信号依次输出到多个初始化线gil1~giln。

[0097]

栅极驱动块gdb基于栅极控制信号gds生成多个发光信号以及多个发光初始化信号。栅极驱动块gdb将发光信号依次输出到多个发光线eml1~emln,并将发光初始化信号依次输出到多个发光初始化线ebl1~ebln。

[0098]

电压生成块vgb从控制器cp接收电压控制信号vcs。电压生成块vgb生成显示面板dp的工作所需的电压。作为本发明的一例,电压生成块vgb生成第一驱动电压elvdd、第二驱动电压elvss以及初始化电压vinit。电压生成块vgb可以根据控制器cp的控制来工作。作为本发明的一例,第一驱动电压elvdd的电压电平大于第二驱动电压elvss的电压电平。作为本发明的一例,第一驱动电压elvdd的电压电平可以是20v至30v。初始化电压vinit的电压电平小于第二驱动电压elvss的电压电平。作为本发明的一例,初始化电压vinit的电压电平可以是1v至9v。

[0099]

作为本发明的一例,显示面板dp包括多个扫描线gwl1~gwln、多个补偿线gcl1~gcln、多个初始化线gil1~giln、多个发光线eml1~emln、多个发光初始化线ebl1~ebln、多个数据线dl1~dlm以及多个像素px11~pxnm。

[0100]

扫描线gwl1~gwln、补偿线gcl1~gcln、初始化线gil1~giln、发光线eml1~emln以及发光初始化线ebl1~ebln向第一方向dr1延伸,并向第二方向dr2排列成彼此隔开。数据线dl1~dlm从源极驱动块sdb向第二方向dr2的相反方向延伸,并向第一方向dr1排列成彼此隔开。

[0101]

像素px11~pxnm的每一个接通到信号线gwl1~gwln、gcl1~gcln、gil1~giln、eml1~emln、ebl1~ebln中的相对应的信号线。根据像素px11~pxnm的驱动电路的构成,像素px11~pxnm和信号线gwl1~gwln、gcl1~gcln、gil1~giln、eml1~emln、ebl1~ebln的连接关系可以发生改变。作为本发明的一例,像素px11~pxnm可以配置在显示面板dp的显示区域da(参照图2)中。

[0102]

作为本发明的一例,显示面板dp包括第一电源线rl1、第二电源线rl2以及初始化

电源线ql。像素px11~pxnm的每一个电连接到第一电源线rl1、第二电源线rl2以及初始化电源线ql。第一电源线rl1从电压生成块vgb接收第一驱动电压elvdd。第二电源线rl2从电压生成块vgb接收第二驱动电压elvss。初始化电源线ql从电压生成块vgb接收初始化电压vinit。

[0103]

像素px11~pxnm可以包括具有生成彼此不同的颜色光的有机发光二极管的多个组。例如,可以包括生成红颜色光的红色像素、生成绿颜色光的绿色像素以及生成蓝颜色光的蓝色像素。红色像素的发光二极管、绿色像素的发光二极管以及蓝色像素的发光二极管可以包括彼此不同物质的发光层。包括在各像素px11~pxnm中的发光二极管可以包括阴极(cathode)ca。阴极ca可以与第二电源线rl2电连接而从电压生成块vgb接收第二驱动电压elvss。替代性地,包括在像素px11~pxnm中的阴极ca也可以彼此一体地形成而形成公共阴极。作为本发明的一例,公共阴极也可以形成为与两个以上的像素重叠。

[0104]

作为本发明的一例,显示面板dp可以还包括分别电连接到数据线dl1~dlm的多个阻抗控制部icu1~icum。阻抗控制部icu1~icum的每一个接通到阻抗控制线icl。作为本发明的一例,阻抗控制部icu1~icum可以配置在源极驱动块sdb和像素px11~pxnm之间。作为本发明的一例,在各个数据线dl1~dlm中,阻抗控制部icu1~icum中的相对应的阻抗控制部和像素可以向第二方向dr2的相反方向排列并连接。

[0105]

作为本发明的一例,栅极驱动块gdb可以包括阻抗控制块icb。阻抗控制块icb可以基于从栅极驱动块gdb生成的扫描信号生成阻抗控制信号ics(参照图7)。阻抗控制块icb通过阻抗控制线icl将阻抗控制信号ics输出到阻抗控制部icu1~icum。然而,作为本发明的一例,阻抗控制块icb可以不包括在栅极驱动块gdb中。面板驱动块pdb也可以包括单独的阻抗控制块。

[0106]

可以通过响应于阻抗控制信号ics控制阻抗控制部icu1~icum来调节数据线dl1~dlm的每一个的阻抗(impedance)。

[0107]

阻抗控制部icu1~icum可以配置在源极驱动块sdb和像素px11~pxnm之间。阻抗控制部icu1~icum可以配置在非显示区域nda中。

[0108]

作为本发明的一例,当源极驱动块sdb经过阻抗控制部icu1~icum向像素px11~pxnm发送数据信号ds时,可以通过由阻抗控制部icu1~icum进行的所述各数据线dl1~dlm的阻抗控制来防止与所述各数据线dl1~dlm连接的像素px11~pxnm的亮度因外部输入tc(参照图1)而失真。将在下面的图7至图13中叙述通过阻抗控制部icu1~icum防止发生像素px11~pxnm的亮度失真。

[0109]

图4中示出了一个数据线中电连接有一个阻抗控制部,但本发明不限于此。作为本发明的一例,一个数据线中也可以电连接有多个阻抗控制部。

[0110]

图5是根据本发明的一实施例的显示模组的一部分区域中的截面图。

[0111]

显示模组dm包括显示面板dp以及输入感测层isp。显示面板dp包括基底层bl、电路元件层dp-cl、显示元件层dp-oled以及封装层enp。

[0112]

作为本发明的一例,基底层bl可以包括合成树脂层。合成树脂层可以包括热固性树脂。基底层bl可以具有多层结构。例如,基底层bl也可以具有合成树脂层、粘合层以及合成树脂层的三层结构。尤其,合成树脂层可以是聚酰亚胺类树脂层,其材料不受特别限制。合成树脂层可以包括丙烯酸类树脂、甲基丙烯酸类树脂、聚异戊二烯、乙烯类树脂、环氧类

树脂、聚氨酯类树脂、纤维素类树脂、硅氧烷类树脂、聚酰胺类树脂以及苝类树脂中的至少任意一个。除此之外,基底层bl可以包括玻璃基板、金属基板或者有机/无机复合材料基板等。

[0113]

在基底层bl的上面可以配置至少一个无机层。无机层可以包括铝氧化物、钛氧化物、硅氧化物、硅氮氧化物、锆氧化物以及铪氧化物中的至少一个。无机层可以形成为多层。多层无机层可以构成阻挡层和/或缓冲层。在本实施例中,示出为电路元件层dp-cl包括缓冲层bfl。

[0114]

电路元件层dp-cl可以包括多个中间绝缘层以及半导体图案、导电图案、信号线等。可以通过涂层、蒸镀等的方式形成中间绝缘层、半导体层以及导电层。之后,可以通过光刻的方式选择性地图案化中间绝缘层、半导体层以及导电层。可以通过这种方式形成包括在电路元件层dp-cl中的半导体图案、导电图案、信号线等。

[0115]

电路元件层dp-cl可以包括缓冲层bfl、第一中间绝缘层100、第二中间绝缘层200、第三中间绝缘层300、第四中间绝缘层400、第五中间绝缘层500以及第六中间绝缘层600。

[0116]

缓冲层bfl可以提高基底层bl和半导体图案之间的结合力。缓冲层bfl可以包括硅氧化物层以及硅氮化物层,硅氧化物层和硅氮化物层可以交替层叠。

[0117]

半导体图案可以配置在缓冲层bfl上。半导体图案可以包括多晶硅。但是,实施例不限于此,半导体图案也可以包括非晶硅或者金属氧化物。

[0118]

图5仅示出了一部分的半导体图案,在平面上,在像素的另一区域中可以还配置半导体图案。半导体图案可以跨像素而以特定的规则排列。半导体图案可以根据掺杂与否而电特性不同。半导体图案可以包括导电率高的第一半导体区域和导电率低的第二半导体区域。第一半导体区域可以由n型掺杂剂或者p型掺杂剂掺杂。p型晶体管包括由p型掺杂剂掺杂的掺杂区域。可以是,第二半导体区域是非掺杂区域,或者以与第一半导体区域相比低的浓度掺杂。

[0119]

第一半导体区域的导电性大于第二半导体区域,实质上具有电极或者信号线的作用。第二半导体区域实质上相当于晶体管的沟道(或者有源区)区域。换言之,半导体图案的一部分可以是晶体管的沟道区域,另一部分可以是晶体管的源极区域或者漏极区域,又另一部分可以是连接电极或者连接信号线。

[0120]

如图5所示,晶体管tr的源极区域se、沟道区域ae以及漏极区域de由半导体图案scp_a形成。源极区域se以及漏极区域de可以在截面上从沟道区域ae向彼此相反的方向延伸。图5中示出了由半导体图案scp_a形成的连接信号线csl的一部分。虽然没有单独示出,但是连接信号线csl可以在平面上电连接到晶体管tr的漏极区域de。

[0121]

在缓冲层bfl上配置第一中间绝缘层100。第一中间绝缘层100与多个像素共同重叠,并覆盖半导体图案scp_a。第一中间绝缘层100可以是无机层和/或有机层,可以具有单层或者多层结构。第一中间绝缘层100可以包括铝氧化物、钛氧化物、硅氧化物、硅氮氧化物、锆氧化物以及铪氧化物中的至少一个。在本实施例中,第一中间绝缘层100可以是单层的硅氧化物层。除了第一中间绝缘层100之外,将在下面叙述的电路元件层dp-cl的中间绝缘层200、300、400、500、600可以是无机层和/或有机层,可以具有单层或者多层结构。无机层可以包括上述的物质中的至少一个。

[0122]

在第一中间绝缘层100上配置晶体管tr的栅极ge。栅极ge可以是金属图案的一部

分。栅极ge可以与沟道区域ae重叠。在掺杂半导体图案scp_a的工艺中栅极ge可以作为掩模发挥功能。

[0123]

在第一中间绝缘层100上配置覆盖栅极ge的第二中间绝缘层200。第二中间绝缘层200可以与像素共同重叠。第二中间绝缘层200可以是无机层和/或有机层,可以具有单层或者多层结构。在本实施例中,第二中间绝缘层200可以是单层的硅氧化物层。

[0124]

在第二中间绝缘层200上配置上电极ue。上电极ue可以与栅极ge重叠。上电极ue可以是金属图案的一部分。栅极ge的一部分和与其重叠的上电极ue可以定义电容器。在本发明的一实施例中,也可以省略上电极ue。

[0125]

在第二中间绝缘层200上配置覆盖上电极ue的第三中间绝缘层300。第三中间绝缘层300可以与像素共同重叠。第三中间绝缘层300可以是无机层和/或有机层,可以具有单层或者多层结构。在本实施例中,第三中间绝缘层300可以是单层的硅氧化物层。

[0126]

在第三中间绝缘层300上可以配置第一连接电极cne1。第一连接电极cne1可以通过贯通第一至第三中间绝缘层100、200、300的第一接触孔cnt-1而接通到连接信号线csl。

[0127]

在第三中间绝缘层300上可以配置第四中间绝缘层400。第四中间绝缘层400可以是单层的硅氧化物层。

[0128]

在第四中间绝缘层400上配置第五中间绝缘层500。第五中间绝缘层500可以是有机层。在第五中间绝缘层500上可以配置第二连接电极cne2。第二连接电极cne2可以通过贯通第四以及第五中间绝缘层400、500的第二接触孔cnt-2而接通到第一连接电极cne1。

[0129]

在第五中间绝缘层500上配置覆盖第二连接电极cne2的第六中间绝缘层600。第六中间绝缘层600可以是有机层。

[0130]

在电路元件层dp-cl上可以形成显示元件层dp-oled。作为本发明的一例,显示元件层dp-oled可以包括发光元件oled以及像素界定膜pdl。

[0131]

发光元件oled可以包括配置在电路元件层dp-cl上的阳极an、配置在阳极an上的发光层eml以及配置在发光层eml上的阴极ca。

[0132]

在第六中间绝缘层600上配置阳极an。阳极an通过贯通第六中间绝缘层600的第三接触孔cnt-3而连接到第二连接电极cne2。

[0133]

可以是,像素界定膜pdl配置在第六中间绝缘层600上,并覆盖阳极an的一部分。在像素界定膜pdl中界定像素开口部。像素开口部暴露阳极an的至少一部分。作为本发明的一例,发光区域pxa可以与由像素开口部暴露的阳极an的一部分区域相对应。非发光区域npxa可以围绕发光区域pxa。

[0134]

在阳极an上配置发光层eml。发光层eml可以配置在与像素开口部相对应的区域中。即,发光层eml可以配置为与像素的每一个分离。发光层eml可以包括发光物质,所述发光物质包括荧光物质或者磷光物质。发光物质可以包括有机发光物质或无机发光物质,不限于任何一个。

[0135]

在发光层eml上配置阴极ca。阴极ca提供为一个公共电极形式而共同配置在多个像素中。

[0136]

作为本发明的一例,发光元件oled可以还包括空穴控制层以及电子控制层。可以是,空穴控制层配置在阳极an和发光层eml之间,还包括空穴注入层。可以是,电子控制层配置在发光层eml和阴极ca之间,还包括电子注入层。

[0137]

封装层enp可以配置在显示元件层dp-oled上。封装层enp可以配置在阴极ca上。

[0138]

封装层enp共同配置在多个像素中。在本实施例中,封装层enp可以直接覆盖阴极ca。在本发明的一实施例中,在封装层enp和阴极ca之间,可以还配置覆盖阴极ca的封盖层。此时,封装层enp可以直接覆盖封盖层。

[0139]

封装层enp可以包括第一无机层iml1、有机层ol以及第二无机层iml2。第一无机层iml1以及第二无机层iml2保护发光元件oled免受水分以及氧气的影响,有机层ol保护发光元件oled免受灰尘粒子之类异物的影响。第一无机层iml1以及第二无机层iml2可以包括硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或者铝氧化物层等。有机层ol可以包括丙烯酸系列有机层,但不限于此。

[0140]

第一无机层iml1可以配置在发光元件oled上。有机层ol配置在第一无机层iml1上。第二无机层iml2可以配置在有机层ol上。

[0141]

输入感测层isp可以形成在显示面板dp上。输入感测层isp可以包括基底绝缘层bil、第一导电层cl1、第一感测绝缘层sil1、第二导电层cl2以及第二感测绝缘层sil2。作为本发明的一例,第一以及第二感测绝缘层sil1、sil2可以是无机层和/或有机层,可以具有单层或者多层结构。

[0142]

基底绝缘层bil可以直接配置在封装层enp上。例如,基底绝缘层bil可以与第二无机层iml2直接接触。基底绝缘层bil可以具有单层或者多层结构。

[0143]

第一导电层cl1可以配置在基底绝缘层bil上。第一感测绝缘层sil1可以配置在第一导电层cl1上。第一感测绝缘层sil1可以是无机层和/或有机层,可以具有单层或者多层结构。

[0144]

第二导电层cl2可以配置在第一感测绝缘层sil1上。可以是,第一导电层cl1以及第二导电层cl2的每一个具有单层结构,或者具有沿着第三方向dr3层叠的多层结构。单层结构的导电层可以包括电极层或者透明导电层。

[0145]

第一导电层cl1以及第二导电层cl2可以包括第一传感器部ssp1、第二传感器部ssp2、第一连接部cp1(参照图6)、第二连接部cp2等。作为本发明的一例,第一导电层cl1可以包括第二连接部cp2。第二导电层cl2可以包括第一传感器部ssp1、第二传感器部ssp2以及第一连接部cp1(参照图6)。然而,也可以是,在第一导电层cl1中包括第一传感器部ssp1、第二传感器部ssp2以及第一连接部cp1,在第二导电层cl2中包括第二连接部cp2。

[0146]

第二感测绝缘层sil2可以配置在第二导电层cl2上。第二感测绝缘层sil2可以是无机层和/或有机层,可以具有单层或者多层结构。

[0147]

作为本发明的一例,第一以及第二传感器部ssp1、ssp2、第一以及第二连接部cp1(参照图6)、cp2可以配置在非发光区域npxa中。

[0148]

作为本发明的一例,阻抗控制部icu1可以配置在非显示区域nda中。阻抗控制部icu1可以包括控制晶体管ctr以及阻抗部imp。控制晶体管ctr的源极区域cse、沟道区域cae以及漏极区域cde由半导体图案scp_b形成。控制晶体管ctr的源极区域cse以及漏极区域cde可以在截面上从沟道区域cae向彼此相反的方向延伸。在第一中间绝缘层100上配置控制晶体管ctr的栅极cge。控制晶体管ctr的栅极cge可以是金属图案的一部分。栅极cge可以与沟道区域cae重叠。在掺杂半导体图案scp_b的工艺中栅极cge可以作为掩模发挥功能。控制晶体管ctr可以配置在与配置在显示区域da中的晶体管(以下,像素晶体管)tr相同的层

中。

[0149]

作为本发明的一例,阻抗部imp可以包括电阻器(resistor)或者电容器(capacitor)。图5中示出了阻抗部imp包括电阻器。作为本发明的一例,阻抗部imp可以配置在电路元件层dp-cl中。阻抗部imp可以配置在与控制晶体管ctr的半导体图案scp_b或者像素晶体管tr的半导体图案scp_a相同的层中。作为本发明的一例,阻抗部imp可以在形成像素晶体管tr的半导体图案scp_a或者控制晶体管ctr的半导体图案scp_b的工艺中形成。作为本发明的一例,阻抗部imp也可以包括多晶硅或者金属氧化物。然而,阻抗部imp也可以包括金属。当阻抗部imp包括多晶硅或者金属氧化物时,阻抗部imp的电阻的大小可以大于在阻抗部imp包括金属的情况下的电阻的大小。

[0150]

在第三中间绝缘层300上可以配置第三连接电极cne3。第三连接电极cne3可以通过贯通第一至第三中间绝缘层100、200、300的第四接触孔cnt-4而接通到阻抗部imp。

[0151]

在第三中间绝缘层300上可以配置第四中间绝缘层400。在第四中间绝缘层400上可以配置数据线dl。数据线dl可以通过贯通第四中间绝缘层400的第五接触孔cnt-5而接通到第三连接电极cne3。

[0152]

图5中示出了控制晶体管ctr的半导体图案scp_b中的一部分。虽然没有单独示出,但是控制晶体管ctr的半导体图案scp_b可以通过贯通第一至第四中间绝缘层100、200、300、400的接触孔与数据线dl电连接。

[0153]

图6是示出根据本发明的一实施例的输入感测层的构成的平面图。

[0154]

参照图6,根据本发明的一实施例的输入感测层isp包括有效区域aa以及与有效区域aa相邻的非有效区域naa。作为本发明的一例,有效区域aa可以与显示面板dp(参照图2)的显示区域da(参照图2)的至少一部分相对应。

[0155]

可以是,多个感应电极se1_1~se1_5、se2_1~se2_4配置在有效区域aa中,多个信号线sl1_1~sl1_5、sl2_1~sl2_4配置在非有效区域naa中。

[0156]

作为本发明的一例,感应电极se1_1~se1_5、se2_1~se2_4包括发送电极se1_1~se1_5以及接收电极se2_1~se2_4。

[0157]

信号线sl1_1~sl1_5、sl2_1~sl2_4可以包括与发送电极se1_1~se1_5连接的发送信号线sl1_1~sl1_5以及与接收电极se2_1~se2_4连接的接收信号线sl2_1~sl2_4。

[0158]

发送电极se1_1~se1_5和接收电极se2_1~se2_4彼此交叉。发送电极se1_1~se1_5向第一方向dr1的相反方向排列,各自向第二方向dr2延伸。接收电极se2_1~se2_4向第二方向dr2排列,且各自向第一方向dr1延伸。

[0159]

所述的输入感测层isp可以以互电容(mutual-cap)方式获取坐标信息。在发送电极se1_1~se1_5和接收电极se2_1~se2_4之间形成电容。发送电极se1_1~se1_5和接收电极se2_1~se2_4之间的电容可以通过由用户us(参照图1)的身体引起的外部输入tc(参照图1)而改变。在此,可以根据电容的变化量确定输入感测层isp的感应灵敏度。

[0160]

发送电极se1_1~se1_5的每一个包括配置在有效区域aa中的第一传感器部ssp1以及第一连接部cp1。接收电极se2_1~se2_4的每一个包括配置在有效区域aa中的第二传感器部ssp2以及第二连接部cp2。

[0161]

在一个发送电极中第一传感器部ssp1沿着第二方向dr2排列,在一个接收电极中第二传感器部ssp2沿着第一方向dr1排列。第一连接部cp1的每一个连接相邻的第一传感器

部ssp1,第二连接部cp2的每一个连接相邻的第二传感器部ssp2。

[0162]

发送电极se1_1~se1_5以及接收电极se2_1~se2_4的每一个可以具有网格形状。由于发送电极se1_1~se1_5以及接收电极se2_1~se2_4分别具有网格形状,因此可以减少与包括在显示面板dp(参照图2)中的电极的寄生电容。

[0163]

网格形状的发送电极se1_1~se1_5以及接收电极se2_1~se2_4可以包括银、铝、铜、铬、镍、钛等,但不限于此。

[0164]

发送信号线sl1_1~sl1_5以及接收信号线sl2_1~sl2_4可以配置在非有效区域naa中。

[0165]

输入感测层isp可以包括从发送信号线sl1_1~sl1_5以及接收信号线sl2_1~sl2_4的一端延伸、并配置在非有效区域naa中的输入焊盘i_pd。输入焊盘i_pd可以与发送信号线sl1_1~sl1_5以及接收信号线sl2_1~sl2_4电连接。作为本发明的一例,输入焊盘i_pd可以包括电连接有发送信号线sl1_1~sl1_5的发送输入焊盘i_pd1以及电连接有接收信号线sl2_1~sl2_4的接收输入焊盘i_pd2。

[0166]

显示装置dd(参照图1)可以还包括控制输入感测层isp的驱动的感测控制器icp。

[0167]

作为本发明的一例,感测控制器icp可以与输入感测层isp电连接。感测控制器icp可以通过输入焊盘i_pd与发送信号线sl1_1~sl1_5以及接收信号线sl2_1~sl2_4电连接。

[0168]

感测控制器icp向发送电极se1_1~se1_5发送驱动控制信号dcs,从接收电极se2_1~se2_4接收反映了发送电极se1_1~se1_5和接收电极se2_1~se2_4之间的电容变化量的感应信号rs。作为本发明的一例,驱动控制信号dcs可以是依次发送给发送电极se1_1~se1_5的每一个的感应扫描信号。

[0169]

参照图4至图6,第一传感器部ssp1以及第二传感器部ssp2可以与阴极ca重叠。在第一传感器部ssp1以及第二传感器部ssp2和阴极ca之间可以产生寄生电容。因此,当通过输入感测层isp感应用户us(参照图1)的外部输入tc(参照图1)时,由于驱动控制信号dcs或者感应信号rs而在阴极ca中可能感应噪声(noise)电压。

[0170]

数据线dl1~dlm以及第一电源线rl1可以与阴极ca重叠。在各个数据线dl1~dlm以及第一电源线rl1和阴极ca之间可能产生寄生电容。因此,通过由于外部输入tc而在阴极ca中感应的噪声成分,可能在各个数据线dl1~dlm以及第一电源线rl1中感应噪声电压。将在下面的图7至图13中叙述由于在各个数据线dl1~dlm以及第一电源线rl1中感应的噪声电压而引起的像素px11~pxnm的亮度失真的发生以及用于防止发生所述的亮度失真的阻抗控制部icu1~icum的构成以及工作。

[0171]

图7是根据本发明的一实施例的像素的电路图,图8是用于驱动图7所示的像素的驱动信号的波形图。图9是用于说明根据本发明的一实施例的阻抗控制块的工作的驱动信号的波形图。

[0172]

参照图7,示例性示出了连接到扫描线gwl1~gwln中的第i扫描线gwli并连接到数据线dl1~dlm中的第j数据线dlj的像素pxij。

[0173]

在本实施例中,像素pxij可以包括第一至第七晶体管tr1~tr7以及像素电容器cst。在本实施例中,说明为第一至第七晶体管tr1~tr7分别是p型晶体管。然而,不限于此,第一至第七晶体管tr1~tr7可以实现为p型晶体管或者n型晶体管中的任意一个。另外,作为另一例,第一至第七晶体管tr1~tr7中的一部分晶体管可以是p型晶体管,其余一部分晶

体管可以是n型晶体管。另外,包括在像素pxij中的晶体管的个数不限于此。即,可以省略第一至第七晶体管tr1~tr7中的至少一个,另外,作为另一例,一个以上的晶体管可以添加到所述的像素pxij。

[0174]

在本实施例中,第一晶体管tr1可以是驱动晶体管,第二晶体管tr2可以是开关晶体管。像素电容器cst接通在接收第一驱动电压elvdd的第一电源线rl1和基准节点rn之间。像素电容器cst包括接通到基准节点rn的第一电极cst_1以及接通到第一电源线rl1的第二电极cst_2。以下,第一至第七晶体管tr1~tr7包括第一电极、第二电极以及控制电极,第一电极指代为源极,第二电极指代为漏极,控制电极指代为栅极。

[0175]

第一晶体管tr1接通在第一电源线rl1和发光元件oled之间。第一晶体管tr1的源极s1与第一电源线rl1电连接。在本说明书中,“晶体管接通到信号线”意指“晶体管的源极、漏极、栅极中的任意一个与信号线具有一体的形状,或者通过连接电极连接”。另外,“晶体管与另一晶体管电连接”意指“晶体管的源极、漏极、栅极中的任意一个电极与另一晶体管的源极、漏极、栅极中的任意一个具有一体的形状,或者通过连接电极连接”。

[0176]

在第一晶体管tr1的源极s1和第一电源线rl1之间可以配置或省略另一晶体管。

[0177]

第一晶体管tr1的漏极d1与发光元件oled的阳极an电连接。在第一晶体管tr1的漏极d1和发光元件oled的阳极an之间可以配置或省略另一晶体管。第一晶体管tr1的栅极g1电连接到基准节点rn。

[0178]

第二晶体管tr2接通在第j数据线dlj和第一晶体管tr1的源极s1之间。可以是,第二晶体管tr2包括第一电极、第二电极以及控制电极,第一电极是源极s2,第二电极是漏极d2,控制电极是栅极g2。第二晶体管tr2的源极s2电连接到第j数据线dlj,第二晶体管tr2的漏极d2电连接到第一晶体管tr1的源极s1。在本实施例中,第二晶体管tr2的栅极g2可以电连接到第i扫描线gwli。

[0179]

第三晶体管tr3接通在基准节点rn和第一晶体管tr1的漏极d1之间。可以是,第三晶体管tr3包括第一电极、第二电极以及控制电极,第一电极是源极s3,第二电极是漏极d3,控制电极是栅极g3。第三晶体管tr3的源极s3电连接到第一晶体管tr1的漏极d1,第三晶体管tr3的漏极d3电连接到基准节点rn。在本实施例中,第三晶体管tr3的栅极g3可以电连接到第i补偿线gcli。

[0180]

第四晶体管tr4接通在第一晶体管tr1的漏极d1和初始化电源线ql之间。可以是,第四晶体管tr4包括第一电极、第二电极以及控制电极,第一电极是源极s4,第二电极是漏极d4,控制电极是栅极g4。第四晶体管tr4的源极s4电连接到初始化电源线ql,第四晶体管tr4的漏极d4电连接到第一晶体管tr1的漏极d1。在本实施例中,第四晶体管tr4的栅极g4可以电连接到第i初始化线gili。在本实施例中,第三晶体管tr3以及第四晶体管tr4可以包括多个栅极。由于第三以及第四晶体管tr3、tr4具有多个栅极,因此可以减少像素pxij的泄漏电流。

[0181]

第五晶体管tr5接通在第一电源线rl1和第一晶体管tr1的源极s1之间。可以是,第五晶体管tr5包括第一电极、第二电极以及控制电极,第一电极是源极s5,第二电极是漏极d5,控制电极是栅极g5。第五晶体管tr5的源极s5电连接到第一电源线rl1,第五晶体管tr5的漏极d5电连接到第一晶体管tr1的源极s1。在本实施例中,第五晶体管tr5的栅极g5可以电连接到第i发光线emli。

[0182]

第六晶体管tr6接通在第一晶体管tr1的漏极d1和发光元件oled之间。可以是,第六晶体管tr6包括第一电极、第二电极以及控制电极,第一电极是源极s6,第二电极是漏极d6,控制电极是栅极g6。第六晶体管tr6的源极s6电连接到第一晶体管tr1的漏极d1,第六晶体管tr6的漏极d6电连接到发光元件oled的阳极an。在本实施例中,第六晶体管tr6的栅极g6可以电连接到第i发光线emli。

[0183]

第七晶体管tr7接通在发光元件oled的阳极an和初始化电源线ql之间。可以是,第七晶体管tr7包括第一电极、第二电极以及控制电极,第一电极是源极s7,第二电极是漏极d7,控制电极是栅极g7。第七晶体管tr7的源极s7电连接到初始化电源线ql,第七晶体管tr7的漏极d7电连接到发光元件oled的阳极an。在本实施例中,第七晶体管tr7的栅极g7可以电连接到第i发光初始化线ebli。第七晶体管tr7可以接收第i发光初始化信号ebi。

[0184]

第j阻抗控制部icuj可以电连接到第j数据线dlj。第j阻抗控制部icuj可以接通在源极驱动块sdb(参照图4)和像素pxij之间。

[0185]

第j阻抗控制部icuj可以通过阻抗控制线icl接收阻抗控制信号ics。

[0186]

图8示出了任意一个帧时段中的一部分。参照图4以及图8,显示装置dd在每个帧时段显示图像im(参照图1)。在一个帧时段期间,扫描线gwl1~gwln、补偿线gcl1~gcln、初始化线gil1~giln、发光线eml1~emln以及发光初始化线ebl1~ebln的每一个依次被扫描。

[0187]

参照图7以及图8,可以是,第i信号gii、gci、gwi、ebi以及第i发光信号emi的每一个在一部分时段期间具有高电平,并在一部分时段期间具有低电平。此时,n型晶体管在相对应的信号具有高电平时导通,p型晶体管在相对应的信号具有低电平时导通。以下,在本发明的实施例中,说明为包括在像素pxij中的第一至第七晶体管tr1~tr7是p型晶体管。第i发光信号emi的高电平时段定义为非发光时段emw_1,第i发光信号emi的低电平时段定义为发光时段emw_2。

[0188]

在一个帧(1frame)的非发光时段emw_1中,第i初始化扫描信号gii供应到第i初始化线gili。将第i初始化扫描信号gii的低电平时段定义为初始化时段giw。若在初始化时段giw中第四晶体管tr4导通,则初始化电压vinit通过第四晶体管tr4传输到第一晶体管tr1的漏极d1。

[0189]

接着,第i补偿扫描信号gci供应到第i补偿线gcli。将第i补偿扫描信号gci的低电平时段定义为补偿时段gcw。补偿时段gcw包括与初始化时段giw重叠的第一时段gcw_1以及与初始化时段giw不重叠的第二时段gcw_2。若在第一时段gcw_1中第三晶体管tr3导通,则初始化电压vinit通过导通的第三晶体管tr3传输到第一晶体管tr1的栅极g1。因此,与第一晶体管tr1的栅极g1连接的基准节点rn初始化为初始化电压vinit。在其之后,在第二时段gcw_2中,第三晶体管tr3保持导通状态,第四晶体管tr4截止。

[0190]

接着,第i扫描信号gwi供应到第i扫描信号线gwli。将第i扫描信号gwi的低电平时段定义为扫描时段gww。若在扫描时段gww中第二晶体管tr2导通,则与数据信号ds相对应的数据电压(vdata)通过第二晶体管tr2传输到第一晶体管tr1的源极s1。此时,所述的第二时段gcw_2和扫描时段gww重叠。第一晶体管tr1通过在第二时段gcw_2中导通的第三晶体管tr3二极管连接,并正向偏置。那么,从施加到第一晶体管tr1的源极s1的数据电压(vdata)减少了第一晶体管tr1的阈值电压(vth)的补偿电压(vdata-vth)施加到第一晶体管tr1的栅极g1。因此,与第一晶体管tr1的栅极g1连接的基准节点rn的电压可以成为补偿电压

(vdata-vth)。此时,可以是,第一驱动电压elvdd和补偿电压(vdata-vth)施加到像素电容器cst的两端,在像素电容器cst中存储与两端电压差(elvdd-(vdata-vth))相对应的电荷。因此,第一晶体管tr1导通,第一晶体管tr1导通的状态通过存储在像素电容器cst中的电荷保持。

[0191]

接着,第i发光初始化信号ebi供应到第i发光初始化线ebli。将第i发光初始化信号ebi的低电平时段称为发光初始化时段ebw。若在发光初始化时段ebw中第七晶体管tr7导通,则初始化电压vinit通过第七晶体管tr7供应到发光元件oled的阳极an。通过将初始化电压vinit施加到发光元件oled的阳极an,可以防止发光元件oled在发光元件oled的驱动初期由于在发光元件oled的阳极an中残留的电压而瞬间以高亮度发光。

[0192]

之后,使得电连接有第i发光线emli的晶体管导通的第i发光信号emi供应到栅极,将其称为发光时段emw_2。在发光时段emw_2期间,第五晶体管tr5以及第六晶体管tr6导通。那么,根据第一晶体管tr1的栅极g1的栅极电压和源极s1的源极电压之间的电压差产生驱动电流i_oled,驱动电流i_oled通过第五以及第六晶体管tr5、tr6供应到发光元件oled而电流流过发光元件oled。可以是,根据第一晶体管tr1的电流-电压关系,第一晶体管tr1的驱动电流i_oled与从第一晶体管tr1的栅极-源极电压(vgs)减去第一晶体管tr1的阈值电压(vth)所得值的二次方(elvdd-vdata)2成正比。由此,驱动电流i_oled可以与第一晶体管tr1的阈值电压(vth)无关地确定。

[0193]

此时,根据由于外部输入tc在第j数据线dlj和第一电源线rl1中感应的噪声成分,流过发光元件oled的驱动电流i_oled的大小可能不同。具体地,第j数据线dlj的阻抗和第一电源线rl1的阻抗可能彼此不同。第j数据线dlj的阻抗可能小于第一电源线rl1的阻抗。其可能因为是,在第j数据线dlj和发光元件oled的阴极ca之间产生的寄生电容的大小小于在第一电源线rl1和发光元件oled的阴极ca之间产生的寄生电容的大小。

[0194]

确定流过发光元件oled的驱动电流i_oled的大小的第一晶体管tr1的栅极电压由施加到像素电容器cst的两端的数据电压(vdata)和第一驱动电压elvdd确定。此时,当第j数据线dlj的阻抗的大小和第一电源线rl1的阻抗的大小彼此不同时,由通过外部输入tc感应的噪声成分引起的第j数据线dlj的数据电压(vdata)的第一变化量(“v1”)和第一驱动电压elvdd的第二变化量(“v2”)可能彼此不同。作为本发明的一例,当第j数据线dlj的阻抗的大小小于第一电源线rl1的阻抗的大小时,第一变化量(“v1”)可能小于第二变化量(“v2”)。因此,在像素电容器cst中可能存储与(elvdd-(vdata-vth) v3)相对应的电荷,所述(elvdd-(vdata-vth) v3)反映了第一变化量(“v1”)和第二变化量(“v2”)的差值(“v3”)。因此,与不存在通过外部输入tc感应的噪声成分的情况相比,流过发光元件oled的驱动电流i_oled的大小发生变化,发光元件oled的亮度可能发生失真。为了防止所述的发光元件oled的亮度发生失真,可以将第j阻抗控制部icuj连接到第j数据线dlj。

[0195]

参照图9,扫描信号gw1~gwn依次扫描到扫描线gwl1~gwln(参照图4)。

[0196]

可以将一个扫描信号扫描到一个扫描线的时段定义为线时段lw。线时段lw包括扫描时段gww以及空白时段blk。作为本发明的一例,在扫描时段gww期间低电平的第一扫描信号gw1发送到第一扫描线gwl1(参照图4),在空白时段blk中高电平的第一扫描信号gw1发送到第一扫描线gwl1。此后,在下一个线时段lw的扫描时段gww期间低电平的第二扫描信号gw2发送到第二扫描线gwl2(参照图4),在空白时段blk中高电平的第二扫描信号gw2发送到

第二扫描线gwl2。

[0197]

可以是,阻抗控制信号ics在一部分时段期间具有高电平,在一部分时段期间具有低电平。以下,将阻抗控制信号ics的工作说明说明为响应于阻抗控制信号ics而控制的阻抗控制部icu1~icum(参照图4)的每一个包括p型的控制晶体管ctr(参照图5)。

[0198]

当各阻抗控制部icu1~icum包括p型的控制晶体管ctr时,阻抗控制信号ics的高电平时段定义为控制时段cw,阻抗控制信号ics的低电平时段定义为非控制时段ncw。另一方面,当各阻抗控制部icu1~icum包括n型的控制晶体管ctr时,阻抗控制信号ics的高电平时段定义为非控制时段ncw,阻抗控制信号ics的低电平时段定义为控制时段cw。

[0199]

作为本发明的一例,阻抗控制信号ics的控制时段cw可以与扫描信号gw1~gwn的扫描时段gww重叠。扫描信号gw1~gwn的扫描时段gww可以包括在阻抗控制信号ics的控制时段cw中。作为本发明的一例,控制时段cw的宽度可以大于或等于各个扫描时段gww的宽度。作为本发明的一例,控制时段cw的宽度可以小于线时段lw的宽度。作为本发明的一例,控制时段cw的宽度和非控制时段ncw的宽度之和可以等于线时段lw的宽度。

[0200]

将在下面的针对图10至图13的说明中叙述阻抗控制部icu1~icum的结构以及响应于阻抗控制信号ics的阻抗控制部icu1~icum的工作。

[0201]

图10a至图10c是用于说明包括电阻部的阻抗控制部的结构的电路图。

[0202]

参照图10a,示例性示出了电连接到第j数据线dlj的第j阻抗控制部icuj_a。

[0203]

作为本发明的一例,第j阻抗控制部icuj_a可以包括第一控制晶体管ctr1以及电阻部rp。在本实施例中,说明为第一控制晶体管ctr1是p型晶体管。然而,不限于此,第一控制晶体管ctr1可以是n型晶体管。

[0204]

第一控制晶体管ctr1电连接到第j数据线dlj。第一控制晶体管ctr1可以串联连接到第j数据线dlj。第一控制晶体管ctr1包括第一电极、第二电极以及控制电极,第一电极指代为源极cs1,第二电极指代为漏极cd1,控制电极指代为栅极cg1。

[0205]

第一控制晶体管ctr1的源极cs1与源极驱动块sdb(参照图4)电连接。第一控制晶体管ctr1的漏极cd1与第j列的像素电连接。第一控制晶体管ctr1的栅极cg1与阻抗控制线icl1电连接。

[0206]

作为本发明的一例,电阻部rp可以与第一控制晶体管ctr1并联连接。可以是,电阻部rp的第一端与第一控制晶体管ctr1的源极cs1电连接,电阻部rp的第二端与第一控制晶体管ctr1的漏极cd1电连接。作为本发明的一例,电阻部rp可以包括主电阻mr。

[0207]

作为本发明的一例,主电阻mr的大小可以是几至几十kω。作为本发明的一例,主电阻mr的大小可以是7kω。然而,主电阻mr的大小可以根据显示装置dd(参照图1)的大小以及包括在显示面板dp(参照图4)中的像素px11~pxnm(参照图4)的配置等而不同。

[0208]

参照图4、图9以及图10a,作为本发明的一例,阻抗控制信号ics(参照图7)包括第一控制信号ics1。第一控制信号ics1供应到阻抗控制线icl1。若在控制时段cw中第一控制晶体管ctr1截止,则供应到第j数据线dlj的数据信号ds通过主电阻mr流动。若在非控制时段ncw中第一控制晶体管ctr1导通,则供应到第j数据线dlj的数据信号ds通过第一控制晶体管ctr1流动。可以是,与第j数据线dlj连接的第j阻抗控制部icuj_a在控制时段cw中具有第一阻抗,在非控制时段ncw中具有第二阻抗。作为本发明的一例,第一阻抗可以大于第二阻抗。

[0209]

因此,可以通过第j阻抗控制部icuj_a调节第j数据线dlj的阻抗。具体地,在控制时段cw中,可以使得第j数据线dlj具有包括主电阻mr的阻抗值。基于此,可以通过使得第j数据线dlj的阻抗的大小和第一电源线rl1的阻抗的大小相同,防止发生由通过外部输入tc(参照图1)感应的噪声成分引起的第j列的像素的亮度失真。

[0210]

参照图10b,电阻部rp_a可以包括主电阻mr以及多个电阻调节部rcp1_a、rcp2_a、rcp3_a。以下,对于与在图10a中说明的构成相同的构成赋予相同的附图标记,并省略重复的说明。

[0211]

多个电阻调节部rcp1_a、rcp2_a、rcp3_a可以接通在第一控制晶体管ctr1的源极cs1和漏极cd1之间。

[0212]

电阻调节部rcp1_a、rcp2_a、rcp3_a的每一个可以包括子电阻sr1_a、sr2_a、sr3_a以及子晶体管str1_a、str2_a、str3_a。

[0213]

作为本发明的一例,电阻调节部rcp1_a、rcp2_a、rcp3_a可以包括第一电阻调节部rcp1_a、第二电阻调节部rcp2_a以及第三电阻调节部rcp3_a。

[0214]

第一电阻调节部rcp1_a包括与主电阻mr并联连接的第一子电阻sr1_a以及连接在主电阻mr和第一子电阻sr1_a之间的第一子晶体管str1_a。第一子晶体管str1_a的源极ss1_a与第一子电阻sr1_a电连接。第一子晶体管str_1a的漏极sd1_a与主电阻mr电连接。第一子晶体管str1_a的控制电极sg1_a与第一电阻控制线rcl1连接,并响应于第一电阻控制信号rcs1而被控制。

[0215]

第二电阻调节部rcp2_a包括与主电阻mr并联连接的第二子电阻sr2_a以及连接在主电阻mr和第二子电阻sr2_a之间的第二子晶体管str2_a。第二子晶体管str2_a的源极ss2_a与第二子电阻sr2_a电连接。第二子晶体管str2_a的漏极sd2_a与主电阻mr电连接。第二子晶体管str2_a的控制电极sg2_a与第二电阻控制线rcl2连接,并响应于第二电阻控制信号rcs2而被控制。

[0216]

第三电阻调节部rcp3_a包括与主电阻mr并联连接的第三子电阻sr3_a以及连接在主电阻mr和第三子电阻sr3_a之间的第三子晶体管str3_a。第三子晶体管str3_a的源极ss3_a与第三子电阻sr3_a电连接。第三子晶体管str3_a的漏极sd3_a与主电阻mr电连接。第三子晶体管str3_a的控制电极sg3_a与第三电阻控制线rcl3连接,并响应于第三电阻控制信号rcs3而被控制。

[0217]

第j阻抗控制部icuj_b的阻抗可以通过第一至第三电阻控制信号rcs1、rcs2、rcs3控制。因此,第j数据线dlj的阻抗也可以通过第一至第三电阻控制信号rcs1、rcs2、rcs3控制。

[0218]

参照图10c,电阻部rp_b可以包括主电阻mr以及多个电阻调节部rcp1_b、rcp2_b、rcp3_b。作为本发明的一例,电阻调节部rcp1_b、rcp2_b、rcp3_b可以包括第一电阻调节部rcp1_b、第二电阻调节部rcp2_b以及第三电阻调节部rcp3_b。以下,对于与在图10a以及图10b中说明的构成相同的构成,赋予相同的附图标记,并省略重复的说明。

[0219]

第二电阻调节部rcp2_b包括与第一子电阻sr1_b并联连接的第二子电阻sr2_b以及连接在第一子电阻sr1_b和第二子电阻sr2_b之间的第二子晶体管str2_b。第二子晶体管str2_b的源极ss2_b与第二子电阻sr2_b电连接。第二子晶体管str2_b的漏极sd2_b与第一子电阻sr1_b电连接。第二子晶体管str2_b的控制电极sg2_b与第二电阻控制线rcl2连接,

并响应于第二电阻控制信号rcs2而被控制。

[0220]

第三电阻调节部rcp3_b包括与第二子电阻sr2_b并联连接的第三子电阻sr3_b以及连接在第二子电阻sr2_b和第三子电阻sr3_b之间的第三子晶体管str3_b。第三子晶体管str3_b的源极ss3_b与第三子电阻sr3_b电连接。第三子晶体管str3_b的漏极sd3_b与第二子电阻sr2_b电连接。第三子晶体管str3_b的控制电极sg3_b与第三电阻控制线rcl3连接,并响应于第三电阻控制信号rcs3而被控制。

[0221]

图11以及图12是用于说明包括电阻部以及电容器的阻抗控制部的结构的电路图。

[0222]

参照图11,作为本发明的一例,阻抗控制信号ics(参照图7)还包括第二控制信号ics2。

[0223]

第j阻抗控制部icuj_d可以还包括第一控制晶体管ctr1、主电阻mr、第二控制晶体管ctr2以及像素电容器icst。以下,对于与在图10a中说明的构成以及信号相同的构成以及信号,赋予相同的附图标记,并省略重复的说明。

[0224]

第二控制晶体管ctr2电连接到第j数据线dlj。第二控制晶体管ctr2可以并联连接到第j数据线dlj。第二控制晶体管ctr2包括第一电极、第二电极以及控制电极,第一电极指代为源极cs2,第二电极指代为漏极cd2,控制电极指代为栅极cg2。

[0225]

作为本发明的一例,像素电容器icst可以电连接到第二控制晶体管ctr2。第二控制晶体管ctr2的源极cs2与第j数据线dlj电连接。第二控制晶体管ctr2的漏极cd2与电容器icst的第一电极icst_1电连接。第二控制晶体管ctr2的栅极cg2与第二阻抗控制线icl2电连接。作为本发明的一例,电容器icst的第二电极icst_2可以与第一电源线rl1(参照图7)电连接。但是,本发明不限于此,第二电极icst_2也可以与第二电源线rl2(参照图7)电连接或接地。

[0226]

作为本发明的一例,电容器icst的电容(capacitance)可以是几至几百皮法(pf)。

[0227]

作为本发明的一例,可以是,第一控制信号ics1在控制时段cw(参照图9)中具有高电平,在非控制时段ncw(参照图9)中具有低电平。可以是,第二控制信号ics2在控制时段cw中具有低电平,在非控制时段ncw中具有高电平。可以是,第一控制晶体管ctr1在控制时段cw中截止,在非控制时段ncw中导通。第二控制晶体管ctr2可以在控制时段cw中导通,在非控制时段ncw中截止。

[0228]

在第一控制信号ics1的控制时段cw和第二控制信号ics2的控制时段cw重叠的重叠时段中,第j数据线dlj可以与主电阻mr以及电容器icst电连接。作为本发明的一例,第一控制信号ics1的控制时段cw的宽度和第二控制信号ics2的控制时段cw的宽度可以彼此相同。

[0229]

参照图12,第j阻抗控制部icuj_e的第二控制晶体管ctr2_a可以是n型晶体管。第二控制晶体管ctr2_a的栅极cg2_a可以与第一阻抗控制线icl1电连接。在此情况下,第一控制晶体管ctr1_a和第二控制晶体管ctr2_a可以通过第一控制信号ics1一起控制。

[0230]

可以是,在第一控制信号ics1的控制时段cw(参照图9)中第一控制晶体管ctr1_a截止,第二控制晶体管ctr2_a导通。可以是,在第一控制信号ics1的非控制时段ncw(参照图9)中第一控制晶体管ctr1_a导通,第二控制晶体管ctr2_a截止。

[0231]

在第一控制信号ics1的控制时段cw中第j数据线dlj可以与主电阻mr以及电容器icst电连接。

[0232]

图13是用于说明包括电容器的阻抗控制部的结构的电路图。

[0233]

参照图13,作为本发明的一例,第j阻抗控制部icuj_f可以包括控制晶体管ctr以及电容器icst。

[0234]

控制晶体管ctr电连接到第j数据线dlj。控制晶体管ctr可以并联连接到第j数据线dlj。控制晶体管ctr包括第一电极、第二电极以及控制电极,第一电极指代为源极cs,第二电极指代为漏极cd,控制电极指代为栅极cg。

[0235]

控制晶体管ctr的源极cs电连接到第j数据线dlj。控制晶体管ctr的漏极cd与电容器icst电连接。控制晶体管ctr的栅极cg与阻抗控制线icl电连接。

[0236]

电容器icst的第一电极icst_1与控制晶体管ctr的漏极cd电连接。电容器icst的第二电极icst_2可以与第一电源线rl1(参照图7)电连接。但是,本发明不限于此,第二电极icst_2也可以与第二电源线rl2(参照图7)电连接或接地。

[0237]

可以是,控制晶体管ctr在控制时段cw(参照图9)中导通,在非控制时段ncw(参照图9)中截止。在阻抗控制信号ics的控制时段cw中,第j数据线dlj可以与电容器icst电连接。

[0238]

与第j数据线dlj连接的第j阻抗控制部icuj_f可以在控制时段cw中具有第一阻抗,在非控制时段ncw中具有第二阻抗。作为本发明的一例,第一阻抗可以大于第二阻抗。

[0239]

以上,参照本发明的优选实施例进行了说明,但对于本技术领域的熟练人员或者在本技术领域中具有通常知识的人员来说,能够理解可以在不超出权利要求书中记载的本发明的构思以及技术领域的范围内对本发明进行各种修改及变更。

[0240]

因此,本发明的技术范围并非由说明书的详细说明中记载的内容来限定,而是应通过权利要求书来确定。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。