1.本技术属于电力电子技术领域,尤其涉及一种带隙基准电路。

背景技术:

2.带隙基准电路是模拟集成电路的重要部分,被广泛应用于几乎所有集成电路中。随着集成电路产业的不断发展,高性能集成系统对带隙基准电路提出了更高的要求。现有的带隙基准电路根据电源模块提供的电源电压产生基准电压信号,其产生的基准电压信号随电源电压变化较大,无法满足高性能集成系统的要求。

技术实现要素:

3.本技术实施例提供了一种带隙基准电路,可以解决现有的带隙基准电路输出的基准电压信号随电源电压变化较大的问题。

4.本技术实施例提供了一种带隙基准电路,包括第一电流产生模块、第一电压产生模块、钳位模块和基准电压产生模块;所述第一电压产生模块分别与所述第一电流产生模块和所述钳位模块电连接,所述钳位模块与所述基准电压产生模块电连接,所述第一电流产生模块、所述第一电压产生模块、所述钳位模块和所述基准电压产生模块均用于与电源模块电连接;所述第一电流产生模块用于根据所述电源模块提供的电源电压产生第一电流信号,并将所述第一电流信号传输至所述第一电压产生模块;所述第一电压产生模块用于根据所述第一电流信号产生第一电压信号,并将所述第一电压信号传输至所述钳位模块;所述钳位模块用于根据所述第一电压信号产生钳位电压信号,并将所述钳位电压信号传输至所述基准电压产生模块;所述基准电压产生模块用于根据所述钳位电压信号产生基准电压信号。

5.一种可能的实现方式中,所述第一电流产生模块包括第一开关管;所述第一开关管的第一导通端用于与所述电源模块的正极电连接,所述第一开关管的控制端分别与所述第一开关管的第二导通端、所述第一电压产生模块和所述钳位模块电连接。

6.一种可能的实现方式中,所述第一开关管为本征nmos晶体管。

7.一种可能的实现方式中,所述第一电压产生模块包括第二开关管和第三开关管;所述第二开关管的第一导通端分别与所述第一电流产生模块、所述钳位模块和所述第二开关管的控制端电连接,所述第二开关管的第二导通端分别与所述第三开关管的第一导通端和所述第三开关管的控制端电连接,所述第三开关管的第二导通端与所述电源模块的负极电连接,所述电源模块的负极接地。

8.一种可能的实现方式中,所述钳位模块包括第四开关管;所述第四开关管的控制端分别与所述第一电流产生模块和所述第一电压产生模块电连接,所述第四开关管的第一导通端用于与所述电源模块的正极电连接,所述第四开关管的第二导通端与所述基准电压产生模块电连接。

9.一种可能的实现方式中,所述第四开关管为本征nmos晶体管。

10.一种可能的实现方式中,所述基准电压产生模块包括第二电流产生单元和基准电压产生单元;所述第二电流产生单元分别与所述钳位模块和所述基准电压产生单元电连接,所述基准电压产生单元用于与所述电源模块电连接;所述第二电流产生单元用于根据所述钳位电压信号产生第二电流信号,并将所述第二电流信号传输至所述基准电压产生单元;所述基准电压产生单元用于根据所述第二电流信号产生所述基准电压信号。

11.一种可能的实现方式中,所述第二电流产生单元包括第五开关管;所述第五开关管的第一导通端与所述钳位模块电连接,所述第五开关管的控制端分别与所述第五开关管的第二导通端和所述基准电压产生单元电连接。

12.一种可能的实现方式中,所述第五开关管为本征nmos晶体管。

13.一种可能的实现方式中,所述基准电压产生单元包括第六开关管;所述第六开关管的控制端分别与所述第六开关管的第一导通端和所述第二电流产生单元电连接,所述第六开关管的第二导通端用于与所述电源模块的负极电连接,所述电源模块的负极接地。

14.本技术实施例与现有技术相比存在的有益效果是:本技术实施例提供了一种带隙基准电路,包括第一电流产生模块、第一电压产生模块、钳位模块和基准电压产生模块。第一电压产生模块分别与第一电流产生模块和钳位模块电连接,钳位模块与基准电压产生模块电连接,第一电流产生模块、第一电压产生模块、钳位模块和基准电压生产生模块均用于与电源模块电连接。其中:第一电流产生模块用于根据电源模块提供的电源电压产生第一电流信号,并将第一电流信号传输至第一电压产生模块。第一电压产生模块用于根据第一电流信号产生第一电压信号,并将第一电压信号传输至钳位模块。钳位模块用于根据第一电压信号产生钳位电压信号,并将钳位电压信号传输至基准电压产生模块。基准电压产生模块用于根据钳位电压信号产生基准电压信号。由上可知,本技术实施例提供的带隙基准电路在基准电压产生模块之前设置了钳位模块,通过钳位模块产生了一个相对稳定的钳位电压信号,钳位电压信号随电源电压变化很小,基准电压产生模块根据钳位电压信号产生基准电压信号,基准电压信号随电源电压变化更小,解决了现有的带隙基准电路输出的基准电压信号随电源电压变化较大的问题。

附图说明

15.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

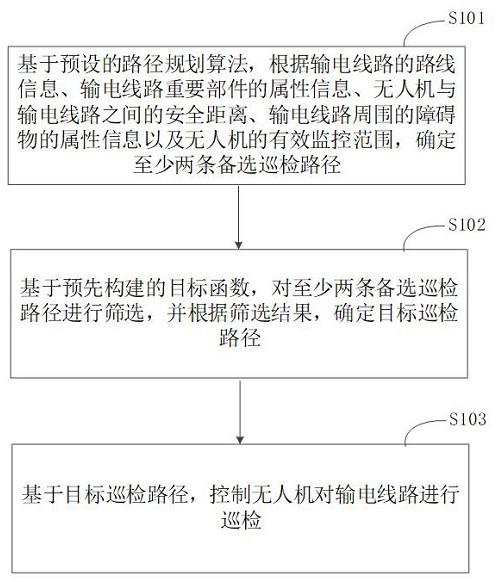

16.图1是现有的带隙基准电路的电路连接示意图;图2是本技术一实施例提供的带隙基准电路的结构示意图;图3是本技术一实施例提供的带隙基准电路的电路连接示意图;图4是本技术另一实施例提供的带隙基准电路的电路连接示意图。

17.图中:100、第一电流产生模块;200、第一电压产生模块;300、钳位模块;400、基准电压产生模块;401、第二电流产生单元;402、基准电压产生单元;500、电源模块。

具体实施方式

18.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本技术实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本技术。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本技术的描述。

19.应当理解,当在本技术说明书和所附权利要求书中使用时,术语“包括”指示所描述特征、整体、步骤、操作、元素和/或组件的存在,但并不排除一个或多个其它特征、整体、步骤、操作、元素、组件和/或其集合的存在或添加。

20.还应当理解,在本技术说明书和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

21.如在本技术说明书和所附权利要求书中所使用的那样,术语“如果”可以依据上下文被解释为“当

…

时”或“一旦”或“响应于确定”或“响应于检测到”。类似地,短语“如果确定”或“如果检测到[所描述条件或事件]”可以依据上下文被解释为意指“一旦确定”或“响应于确定”或“一旦检测到[所描述条件或事件]”或“响应于检测到[所描述条件或事件]”。

[0022]

另外,在本技术说明书和所附权利要求书的描述中,术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

[0023]

在本技术说明书中描述的参考“一个实施例”或“一些实施例”等意味着在本技术的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。术语“包括”、“包含”、“具有”及它们的变形都意味着“包括但不限于”,除非是以其他方式另外特别强调。

[0024]

带隙基准电路作为模拟集成电路的重要部分,随着集成电路产业的不断发展,高性能集成系统对带隙基准电路的精度、温漂和电源抑制比等性能提出了更高的要求,同时低功耗、低成本在实际应用中也是十分必要的。

[0025]

当前现有技术中的带隙基准电路采用运算放大器结构或者共源共栅结构来稳定输出的基准电压信号以改善电源抑制比,但具有功耗高、芯片面积大的缺点,而且运算放大器的噪声和速度也会影响基准电压信号。

[0026]

如图1所示,现有的带隙基准电路仅采用开关管m01和开关管m02,根据电源模块500提供的电源电压输出基准电压信号,其中开关管m01为本征nmos晶体管,开关管m02为nmos晶体管。开关管m01的栅极和源极电连接,由于本征nmos管的阈值电压为负电压,故开关管m01饱和导通,开关管m01在饱和区产生的电流用表示,其中,表示开关管m01的电子迁移率,为一常数,表示开关管m01的栅极氧化层电容,为一常数,表示开关管m01的宽,表示开关管m01的长,表示开关管m01的阈值电压。由上式可见,开关管m01产生的电流由开关管m01的宽长比决定。开关管m02的栅极和漏极电连接,相当于二极管的连接方式,因为其阈值电压大于0,所以,表示开关管m02的漏极与源极之间的

电压,表示开关管m02的栅极与源极之间的电压。由上可知,开关管m02处于饱和导通,开关管m01产生的电流流过开关管m02,开关管m02在饱和区的电流用表示,其中,表示开关管m02的电子迁移率,为一常数,表示开关管m02的栅极氧化层电容,为一常数,表示开关管m02的宽,表示开关管m02的长,表示开关管m02的阈值电压,表示现有的带隙基准电路输出的基准电压信号。则有等式,也可以表示为:=,则可以得到。从上可知,基准电压信号仅与开关管m01和开关管m02的尺寸和工艺有关。为了探究基准电压信号是否和电流有关,把开关管m01的宽控制在5um,对开关管m01的宽长比进行不断的修改,并把开关管m02的宽控制在5um,通过改变开关管m02的长得到零温度系数的基准电压信号,具体数据如表1所示,表1 现有的带隙基准电路的数据表根据表1可知,基准电压信号基本不受电流的影响,较小的电流即可保证较为稳定的基准电压信号。因此选择较小的电流可以使电路产生较低的功耗,且通过限定开关管的宽长比可以得到零温度系数的基准电压信号,同时电路整体面积小,电源抑制比较高,基本满足了高性能集成系统对带隙基准电路的设计要求。但是由于开关管m01和

开关管m02存在沟道调制效应,所以电流和电流都需要分别乘上,其中为沟道调制系数,所以会有等式=,从上述等式可以看出,基准电压信号与电源模块500提供的电源电压有关。因此现有的带隙基准电路输出的基准电压信号随电源电压变化较大,电源抑制比不够理想。

[0027]

需要说明的是,本征nmos晶体管属于本征半导体,本征半导体一般是指其导电能力主要由材料的本征激发决定的纯净半导体。

[0028]

由此,针对现有的带隙基准电路输出的基准电压信号随电源电压变化较大的问题,本技术实施例提出了一种带隙基准电路,如图2所示,带隙基准电路包括:第一电流产生模块100、第一电压产生模块200、钳位模块300和基准电压产生模块400。第一电压产生模块200分别与第一电流产生模块100和钳位模块300电连接,钳位模块300与基准电压产生模块400电连接。第一电流产生模块100、第一电压产生模块200、钳位模块300和基准电压产生模块400均用于与电源模块500电连接。

[0029]

具体的,第一电流产生模块100用于根据电源模块500提供的电源电压产生第一电流信号,并将第一电流信号传输至第一电压产生模块200。第一电压产生模块200用于根据第一电流信号产生第一电压信号,并将第一电压信号传输至钳位模块300。钳位模块300用于根据第一电压信号产生钳位电压信号,并将钳位电压信号传输至基准电压产生模块400。基准电压产生模块400用于根据钳位电压信号产生基准电压信号。

[0030]

由上可知,本技术实施例提供的带隙基准电路在基准电压产生模块400之前设置了钳位模块300,通过钳位模块300产生了一个相对稳定的钳位电压信号,钳位电压信号随电源电压变化很小,基准电压产生模块400根据钳位电压信号产生基准电压信号,基准电压信号随电源电压变化更小,电源抑制比更高,解决了现有的带隙基准电路输出的基准电压信号随电源电压变化较大的问题。

[0031]

如图3所示,第一电流产生模块100包括第一开关管m1。第一开关管m1的第一导通端用于与电源模块500的正极电连接,接收电源模块500提供的电源电压,第一开关管m1的控制端分别与第一开关管m1的第二导通端、第一电压产生模块200和钳位模块300电连接。

[0032]

示例性的,第一开关管m1为本征nmos晶体管,第一开关管m1的控制端为本征nmos晶体管的栅极,第一开关管m1的第一导通端为本征nmos晶体管的漏极,第二开关管m1的第二导通端为本征nmos晶体管的源极。

[0033]

具体的,第一开关管m1的栅极和源极电连接,由于第一开关管m1为本征nmos晶体管且本征nmos晶体管的阈值电压为负电压,故第一开关管m1饱和导通,第一开关管m1在饱和区产生的电流用表示,,表示第一开关管m1的电子迁移率,为一常数,表示第一开关管m1的栅极氧化层电容,为一常数,表示第一开关管m1的宽,表示第一开关管m1的长,表示第一开关管m1的阈值电压。由上式可知,第一开关管m1产生的电流由第一开关管m1的宽长比决定。

[0034]

如图3所示,第一电压产生模块200包括第二开关管m2和第三开关管m3。第二开关

管m2的第一导通端分别与第一电流产生模块100、钳位模块300和第二开关管m2的控制端电连接,第二开关管m2的第二导通端分别与第三开关管m3的第一导通端和第三开关管m3的控制端电连接,第三开关管m3的第二导通端与电源模块500的负极电连接,电源模块500的负极接地。其中第二开关管m2的第一导通端分别与第一电流产生模块100中的第一开关管m1的控制端和第一开关管m1的第二导通端、钳位模块300和第二开关管m2的控制端电连接。

[0035]

示例性的,第二开关管m2和第三开关管m3均为nmos晶体管。第二开关管m2的控制端为nmos晶体管的栅极,第二开关管m2的第一导通端为nmos晶体管的漏极,第二开关管m2的第二导通端为nmos晶体管的源极。第三开关管m3的控制端为nmos晶体管的栅极,第三开关管m3的第一导通端为nmos晶体管的漏极,第三开关管m3的第二导通端为nmos晶体管的源极。

[0036]

具体的,第二开关管m2的栅极与漏极电连接,相当于二极管的连接方式,第三开关管m3的栅极与漏极电连接,也相当于二极管的连接方式,且第三开关管m3的阈值电压大于0,所以,表示第三开关管m3的漏极与源极之间的电压,表示第三开关管m3的栅极与源极之间的电压。由上可知第三开关管m3饱和导通,同时第二开关管m2也饱和导通,第一开关管m1产生的电流流过第三开关管m3,第三开关管m3在饱和区的电流用表示,其中,表示第三开关管m3的电子迁移率,为一常数,表示第三开关管m3的栅极氧化层电容,为一常数,表示第三开关管m3的宽,表示第三开关管m3的长,表示第三开关管m3的阈值电压,表示第三开关管m3的漏极电压。则有等式,也可以表示为:=,得到,其中第一开关管m1的宽长比为5um/8um,第二开关管m2的宽长比为20um/1um,第三开关管m3的宽长比为5um/15.63um,则为零温度系数电压,根据对现有的带隙基准电路的原理解释可知,会随电源电压变化。第二开关管m2会对进行升压,得到第一电压信号,第一电压信号用表示,则,其中表示第二开关管m2的栅极与源极之间的电压。

[0037]

如图3所示,钳位模块300包括第四开关管m4。第四开关管m4的控制端分别与第一电流产生模块100和第一电压产生模块200电连接,第四开关管m4的第一导通端用于与电源模块500的正极电连接,接收电源模块500提供的电源电压,第四开关管m4的第二导通端与基准电压产生模块400电连接。其中第四开关管m4的控制端分别与第一电流产生模块100中的第一开关管m1的控制端、第一开关管m1的第二导通端和第一电压产生模块200中的第二开关管m2的控制端、第二开关管m2的第一导通端电连接。

[0038]

示例性的,第四开关管m4为本征nmos晶体管。第四开关管m4的控制端为本征nmos晶体管的栅极,第四开关管m4的第一导通端为本征nmos晶体管的漏极,第四开关管m4的第二导通端为本征nmos晶体管的源极。

[0039]

具体的,由于第四开关管m4为本征nmos晶体管,且本征nmos晶体管的阈值电压为负电压,所以第四开关管m4在第一电压信号的作用下导通,并输出钳位电压信号,钳位电压信号用表示,则,其中表示第四开关管m4的栅极与源极之间的电压。钳位模块300通过第四开关管m4产生了一个相对稳定的钳位电压信号,该钳位电压信号随电源电压变化已经很小。

[0040]

如图3所示,基准电压产生模块400包括第二电流产生单元401和基准电压产生单元402。第二电流产生单元401分别与钳位模块300和基准电压产生单元402电连接,基准电压产生单元402用于与电源模块500电连接。

[0041]

具体的,第二电流产生单元401用于根据钳位电压信号产生第二电流信号,并将第二电流信号传输至基准电压产生单元402。基准电压产生单元402用于根据第二电流信号产生基准电压信号。由上可知,钳位电压信号随电源电压变化很小,则基准电压信号随电源电压变化更小,电源抑制比更高。

[0042]

如图4所示,第二电流产生单元401包括第五开关管m5。第五开关管m5的第一导通端与钳位模块300电连接,第五开关管m5的控制端分别与第五开关管m5的第二导通端和基准电压产生单元402电连接。其中第五开关管m5的第一导通端与钳位模块300中的第四开光管m4的第二导通端电连接。

[0043]

示例性的,第五开关管m5为本征nmos晶体管。第五开关管m5的控制端为本征nmos晶体管的栅极,第五开关管m5的第一导通端为本征nmos晶体管的漏极,第五开关管m5的第二导通端为本征nmos晶体管的源极。

[0044]

具体的,第五开关管m5的漏极接收钳位电压信号,因此第五开关管m5的漏极被钳位在一个固定电压。第五开关管m5的栅极与源极电连接,且第五开关管m5为本征nmos晶体管,本征noms晶体管的阈值电压为负电压,故第五开关管m5根据钳位电压信号饱和导通,第五开关管m5在饱和区产生的电流用表示,,表示第五开关管m5的电子迁移率,为一常数,表示第五开关管m5的栅极氧化层电容,为一常数,表示第五开关管m5的宽,表示第五开关管m5的长,表示第五开关管m5的阈值电压。由上式可见,第五开关管m5产生的电流由第五开关管m5的宽长比决定。

[0045]

如图4所示,基准电压产生单元402包括第六开关管m6。第六开关管m6的控制端分别与第六开关管m6的第一导通端和第二电流产生单元401电连接,第六开关管m6的第二导通端用于与电源模块500的负极电连接,电源模块500的负极接地。其中第六开关管m6的控制端分别与第六开关管m6的第一导通端和第二电流产生单元401中的第五开关管m5控制端、第五开关管m5的第二导通端电连接。

[0046]

示例性的,第六开关管m6为nmos晶体管。第六开关管m6的控制端为nmos晶体管的栅极,第六开关管m6的第一导通端为nmos晶体管的漏极,第六开关管m6的第二导通端为nmos晶体管的源极。

[0047]

具体的,第六开关管m6的栅极与漏极电连接,相当于二极管的连接方式,且第六开关管m6的阈值电压大于0,所以,表示第六开关管m6的漏极

与源极之间的电压,表示第六开关管m6的栅极与源极之间的电压。由上可知第六开关管m6饱和导通,第五开关管m5产生的电流流过第六开关管m6,第六开关管m6在饱和区的电流用表示,其中,表示第六开关管m6的电子迁移率,为一常数,表示第六开关管m6的栅极氧化层电容,为一常数,表示第六开关管m6的宽,表示第六开关管m6的长,表示第六开关管m6的阈值电压,表示基准电压产生单元402产生的基准电压信号。则有等式=,也可以表示为:=,得到,其中第四开关管m4的宽长比为11.49um/1.6um,第五开关管m5的宽长比为10um/16um,第六开关管m6的宽长比为5um/16.07um,则为零温度系数电压。由上可知,基准电压信号仅与第五开关管m5和第六开关管m6的尺寸和工艺有关。根据上述对现有的带隙基准电路的原理解释可知,开关管存在沟道调制效应,所以电流和电流都需要分别乘上,所以会有等式=,其中为钳位电压信号,钳位电压信号随电源电压变化很小,所以基准电压信号随电源电压变化更小,电源抑制比更高,且基准电压信号基本不受电流的影响,因此通过调整第一开关管m1和第五开关管m5的尺寸即可产生较小的电流,较小的电流可保证较为稳定的基准电压信号,同时使电路产生较低的功耗,且通过限定开关管的宽长比可以得到零温度系数的基准电压信号。整个电路仅采用6个开关管,保证了极小的芯片面积。

[0048]

需要说明的是,本技术基于tsmc(中国的台湾积体电路制造股份有限公司,台积电) 0.25um cmos(complementary metal oxide semiconductor,互补金属氧化物半导体)工艺。

[0049]

本技术实施例提供的带隙基准电路在常温5v电源电压下输出的基准电压信号为1.0379v,在-40℃到120℃的温度范围内,温度系数为8.148ppm/℃,最小的电源电压为1.2v,当电源电压范围为2.3v至5v时,输出的基准电压信号波动小于0.25mv,电源抑制比在低频时为82.0db左右,高频时为53.7db左右,最大功耗小于3.4uw。

[0050]

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述或记载的部分,可以参见其它实施例的相关描述。

[0051]

以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。