1.本技术涉及集成电路技术领域,尤其涉及一种应用于高速时钟处理系统中的可控延时设备。

背景技术:

2.随着集成电路技术的发展,以及人们对数据通信的带宽要求的不断增长,高速以及低功耗已经成为短距离多通道serdes(serializer/deserializer,串行器/解串器)技术的两大主流方向。由于短距离多通道serdes系统中,每个通道的pcb(printed circuit board,印制电路板)走线延时会有失配,同时集成电路制造过程中每个通道之间的光照生产不完全相同,使得接收端的数据以及时钟的相位不完全匹配,导致数据接收端出现误码。

技术实现要素:

3.为至少在一定程度上克服相关技术中每个通道的pcb走线延时会有失配,同时集成电路制造过程中每个通道之间的光照生产不完全相同,使得接收端的数据以及时钟的相位不完全匹配的问题,本技术提供一种应用于高速时钟处理系统中的可控延时设备。

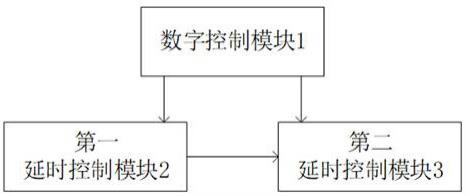

4.本技术的方案如下:一种应用于高速时钟处理系统中的可控延时设备,包括:数字控制模块、第一延时控制模块和第二延时控制模块;所述数字控制模块分别连接所述第一延时控制模块和第二延时控制模块;所述第一延时控制模块的输入端接入时钟信号,输出端连接所述第二延时控制模块的输入端;所述第二延时控制模块的输出端输出时钟信号;所述数字控制模块用于产生数字控制信号;所述第一延时控制模块用于接入数字控制信号中的低位数字控制信号,并根据所述低位数字控制信号对所述时钟信号进行高精度延时控制;所述第二延时控制模块用于接入数字控制信号中的高位数字控制信号,并根据所述高位数字控制信号对所述时钟信号进行低精度延时控制。

5.优选地,所述第一延时控制模块包括:多级第一延时控制单元;所述第二延时控制模块包括:译码器和多级第二延时控制单元;所述译码器用于将所述高位数字控制信号进行译码,并输出译码真值信号。

6.优选地,所述第一延时控制单元包括:第一反相器、第二反相器、第三反相器、第四反相器和开关电容阵列组;所述第一反相器的输入端接入时钟信号,输出端连接所述第二反相器的输入端;所述第二反相器的输出端连接所述开关电容阵列组和所述第三反相器的输入端;所述第三反相器的输出端连接所述第四反相器的输入端;所述第四反相器的输出端输出时钟信号。

7.优选地,所述开关电容阵列组包括多个顺序连接的开关电容阵列,且开关电容阵列中的开关电容个数呈等比数列;所述低位数字控制信号中的各位数字控制信号与所述开关电容阵列组中的各开关电容阵列一一对应。

8.优选地,所述开关电容包括:第一pmos管、第二pmos管、第一nmos管和第二nmos管;所述第二pmos管的栅极连接所述第一pmos管的源极;源极和漏极连接电源;所述第一pmos管的栅极接入所述低位数字控制信号的二进制取反信号;漏极连接所述第一nmos管的漏极;所述第一nmos管的栅极接入所述低位数字控制信号;源极连接所述第二nmos管的栅极;所述第二nmos管的源极和漏极接地。

9.优选地,所述第二延时控制单元包括:第五反相器、第一与非门、第二与非门和第三与非门;所述第五反相器的输入端接入所述译码真值信号;输出端连接所述第一与非门的输入端;所述第一与非门的输入端接入所述时钟信号;输出端连接所述第三与非门的输入端;所述第二与非门的输入端接入所述时钟信号和所述译码真值信号;输出端连接下一级第二延时控制单元中的第一与非门的输入端;所述第三与非门的输入端接入下一级第二延时控制单元中的第三与非门的输出端;输出端输出所述时钟信号。

10.优选地,所述时钟信号经过的第二延时控制单元个数与所述高位数字控制信号的数值正相关。

11.优选地,所述数字控制模块在产生数字控制信号时,所述高位数字控制信号每变化一次,使所述低位数字控制信号循环一个周期。

12.本技术提供的技术方案可以包括以下有益效果:本技术中应用于高速时钟处理系统中的可控延时设备,包括:数字控制模块、第一延时控制模块和第二延时控制模块。数字控制模块分别连接第一延时控制模块和第二延时控制模块;第一延时控制模块的输入端接入时钟信号,输出端连接第二延时控制模块的输入端;第二延时控制模块的输出端输出时钟信号。实施时,数字控制模块产生数字控制信号,第一延时控制模块接入数字控制信号中的低位数字控制信号,并根据低位数字控制信号对时钟信号进行高精度延时控制;第二延时控制模块接入数字控制信号中的高位数字控制信号,并根据高位数字控制信号对时钟信号进行低精度延时控制。本技术中的技术方案,时钟信号首先输入第一延时控制模块,第一延时控制模块用于实现高精度的延时控制,然后再通过第二延时控制模块增加时钟信号整体的延时范围,实现了时钟信号延时控制精度与范围的同时满足,解决了现有技术中接收端的数据以及时钟的相位不完全匹配的问题。

13.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术。

附图说明

14.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本技术的实施例,并与说明书一起用于解释本技术的原理。

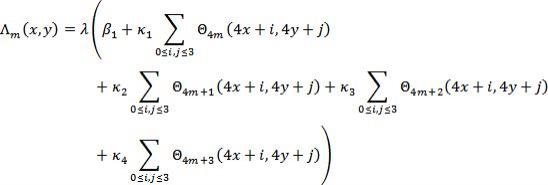

15.图1是本技术一个实施例提供的一种应用于高速时钟处理系统中的可控延时设备的示意框图;图2是本技术一个实施例提供的一种应用于高速时钟处理系统中的可控延时设备的结构示意图;图3是本技术一个实施例提供的一种第一延时控制模块的结构示意图;图4是本技术一个实施例提供的一种第二延时控制模块的结构示意图;图5是本技术一个实施例提供的4位高位数字控制信号与译码真值信号的对应表。

16.附图标记:数字控制模块-1;第一延时控制模块-2;第一延时控制单元-21;第二延时控制模块-3;译码器-31;第二延时控制单元-32;第一反相器-inv1;第二反相器-inv2;第三反相器-inv3;第四反相器-inv4;开关电容阵列组-sca;第一pmos管-mp1;第二pmos管-mp2;第一nmos管-np1;第二nmos管-np2;第五反相器-inv5;第一与非门-nd1;第二与非门-nd2;第三与非门-nd3。

具体实施方式

17.这里将详细地对示例性实施例进行说明,其示例表示在附图中。下面的描述涉及附图时,除非另有表示,不同附图中的相同数字表示相同或相似的要素。以下示例性实施例中所描述的实施方式并不代表与本技术相一致的所有实施方式。相反,它们仅是与如所附权利要求书中所详述的、本技术的一些方面相一致的装置和方法的例子。

18.随着集成电路技术的发展,以及人们对数据通信的带宽要求的不断增长,高速以及低功耗已经成为短距离多通道serdes技术的两大主流方向。由于短距离多通道serdes系统中,每个通道的pcb走线延时会有失配,同时集成电路制造过程中每个通道之间的光照生产不完全相同,使得接收端的数据以及时钟的相位不完全匹配,导致数据接收端出现误码。传统的解决方法是增加时钟数据恢复电路使得接收端的时钟重新锁定数据并恢复数据。然而功耗和面积的增加使得传统的cdr电路很难在低功耗高速多通道serdes中应用。对于高速系统,例如25gb/s,每个bit的周期仅为40ps,传统的数字控制延时单元采用三态门逻辑选择不同数字逻辑门电路的输出,该方法的数字控制延时单元精度较差,最小为一个逻辑门电路的延时时间,即使当下的先进7nm工艺,一个逻辑门的延时时间也达到了5ps,该延时精度已经达到0.125ui,显然无法满足25gb/s的要求。因此合理设计一个数字可控延时单元用于控制时钟与数据之间的失配对于短距离高速低功耗多通道serdes系统具有重要意义。

19.基于此,本实施例提供一种应用于高速时钟处理系统中的可控延时设备,参照图1,包括:数字控制模块1、第一延时控制模块2和第二延时控制模块3;数字控制模块1分别连接第一延时控制模块2和第二延时控制模块3;第一延时控制模块2的输入端接入时钟信号,输出端连接第二延时控制模块3的输入端;第二延时控制模块3的输出端输出时钟信号;

数字控制模块1用于产生数字控制信号;第一延时控制模块2用于接入数字控制信号中的低位数字控制信号,并根据低位数字控制信号对时钟信号进行高精度延时控制;第二延时控制模块3用于接入数字控制信号中的高位数字控制信号,并根据高位数字控制信号对时钟信号进行低精度延时控制。

20.需要说明的是,本实施例中的技术方案涉及集成电路领域,特别是涉及一种应用于高速时钟处理系统中的可控延时设备,可广泛应用于高速串行通信芯片serdes系统中。

21.需要说明的是,参照图2,第一延时控制模块2包括:多级第一延时控制单元21;第二延时控制模块3包括:译码器31和多级第二延时控制单元32;译码器31用于将高位数字控制信号进行译码,并输出译码真值信号。

22.具体的,参照图3,第一延时控制单元21包括:第一反相器inv1、第二反相器inv2、第三反相器inv3、第四反相器inv4和开关电容阵列组sca;第一反相器inv1的输入端接入时钟信号,输出端连接第二反相器inv2的输入端;第二反相器inv2的输出端连接开关电容阵列组sca和第三反相器inv3的输入端;第三反相器inv3的输出端连接第四反相器inv4的输入端;第四反相器inv4的输出端输出时钟信号。

23.具体的,参照图3,开关电容阵列组sca包括多个顺序连接的开关电容阵列,且开关电容阵列中的开关电容个数呈等比数列;低位数字控制信号中的各位数字控制信号与开关电容阵列组sca中的各开关电容阵列一一对应。

24.在具体实践中,开关电容阵列的个数比例可以为4:2:1,对应的,低位数字控制信号包括三位,分别为sw《2》、sw《1》、sw《0》。

25.具体的,参照图3,开关电容包括:第一pmos管mp1、第二pmos管mp2、第一nmos管np1和第二nmos管np2;第二pmos管mp2的栅极连接第一pmos管mp1的源极;源极和漏极连接电源;第一pmos管mp1的栅极接入低位数字控制信号的二进制取反信号;漏极连接第一nmos管np1的漏极;第一nmos管np1的栅极接入低位数字控制信号;源极连接第二nmos管np2的栅极;第二nmos管np2的源极和漏极接地。

26.可以理解的是,本实施例中的clkin指时钟信号输入,clkout指时钟信号输出,sw《2:0》为低位数字控制信号,swb《2:0》为低位数字控制信号的二进制取反信号,取反是java与c/c 使用补码来表示二进制数,在补码表示中,最高位为符号位,正数的符号位为0,负数为1。

27.如图3所示的第一延时控制单元21结构,其中包含4级反向器,其中第二反向器的输出连接开关电容阵列以及第三反向器的输入,开关电容阵列共三组组成,分别由数字控制信号的低三位sw《2:0》控制,swb《2:0》为sw《2:0》取反。sw《2:0》控制的开关电容阵列的个数比例为4:2:1。如图3所示,开关电容包含第一pmos管mp1、第二pmos管mp2、第一nmos管np1和第二nmos管np2。第一pmos管mp1和第一nmos管np1作为开关mos管,当sw=0,swb=1时,两个开关断开,第二pmos管mp2和第二nmos管np2的mos电容无法接入高速链路,此时高速链路的

延时不受任何影响;当sw=1,swb=0时,两个开关闭合,第二pmos管mp2和第二nmos管np2的mos电容接入高速链路,此时第二反相器inv2的输出负载电容变大,上升沿和下降沿均变大,节点的充放电时间变慢,达到延时的效果。第二pmos管mp2和第二nmos管np2的电容大小直接影响着延时精度,电容大小由第二pmos管mp2和第二nmos管np2的尺寸决定,第二pmos管mp2和第二nmos管np2的尺寸越小,延时精度越高。为了减小电源和地的噪声对高速信号的影响,各级反向器输出上升沿和下降沿不能太缓,因此为了不让各级反向器输出上升沿和下降沿太缓,每个节点的开关总电容不能过大。并且为了满足后续低精度时钟信号调节的范围要求,本设计的高精度时钟信号的调节范围也必须满足一定的要求,所以本实施例中采用m级级联的方式,扩大高精度时钟信号的调节范围,每一级第一延时控制单元21均由sw《2:0》和swb《2:0》控制。

28.需要说明的是,参照图4,第二延时控制单元32包括:第五反相器inv5、第一与非门nd1、第二与非门nd2和第三与非门nd3;第五反相器inv5的输入端接入译码真值信号;输出端连接第一与非门nd1的输入端;第一与非门nd1的输入端接入时钟信号;输出端连接第三与非门nd3的输入端;第二与非门nd2的输入端接入时钟信号和译码真值信号;输出端连接下一级第二延时控制单元32中的第一与非门nd1的输入端;第三与非门nd3的输入端接入下一级第二延时控制单元32中的第三与非门nd3的输出端;输出端输出时钟信号。

29.需要说明的是,时钟信号经过的第二延时控制单元32个数与高位数字控制信号的数值正相关。

30.可以理解的是,如图3所示为第二延时控制模块3的结构示意图,由k级第二延时控制单元32以及一个译码器31组成,每级第二延时控制单元32包括三个与非门以及一个反向器。每一级的输出out2连接下一级的in1,下一级的out1连接前一级的in2。本实施例中以图5提供的4位高位数字控制信号与译码真值信号的对应表作为示例性说明。

31.如图5所示,当sw《6:3》=0000时,sel《15:0》=0000000000000001,时钟信号由第一级的in1进入,经过第一与非门nd1和第三与非门nd3由第一级out1输出;当sw《6:3》=0001时,sel《15:0》=0000000000000011,时钟由第一级的in1进入,经过第一级第二与非门nd2、第二级第一与非门nd1和第三与非门nd3、再经过第一级的第三与非门nd3输出。此时相比于sw《6:3》=0000时,时钟信号多经过了两个与非门的延时。依此类推,每当sw《6:3》加1时,时钟均会多经过两个与非门,即时钟信号经过的第二延时控制单元32个数与高位数字控制信号的数值正相关,因此低精度的延时模块的控制精度为两个与非门的延时时间。

32.由此可知,作为低位高精度延时控制模块的第一延时控制模块2的范围应当略小于作为高位低精度延时控制模块的第二延时控制模块3的精度。以7位数字控制信号为例,低3位为高精度控制位,高4位为低精度控制位。sw《6:0》从0000000变化到0000111,高精度延时控制模块延时时间逐渐增大并达到最大范围,低精度延时控制模块为两个与非门的固定延时。总延时时间为两个与非门的固定延时加上高精度延时控制模块的延时。sw《6:0》从0000111变化到0001000,高精度延时控制模块延时时间为0,低精度延时控制模块为固定四

个与非门的延时。sw《6:0》从0001000变化到0001111,总延时时间由固定四个与非门的延时加上高精度延时控制模块的延时时间。依此类推,sw《6:3》每增加1,sw《2:0》循环一次,即数字控制模块1在产生数字控制信号时,高位数字控制信号每变化一次,使低位数字控制信号循环一个周期。低位高精度延时控制模块的范围应当比两个与非门的固定延时小一个高精度延时控制模块的精度时间。这样才能保证高精度与低精度切换时的延时线性度。

33.需要说明的是,本领域技术人员可根据具体系统的延时范围以及精度要求,具体设计整个电路的m、k的级数以及数位控制信号的位数的值。

34.可以理解的是,本实施例中应用于高速时钟处理系统中的可控延时设备,包括:数字控制模块1、第一延时控制模块2和第二延时控制模块3。数字控制模块1分别连接第一延时控制模块2和第二延时控制模块3;第一延时控制模块2的输入端接入时钟信号,输出端连接第二延时控制模块3的输入端;第二延时控制模块3的输出端输出时钟信号。实施时,数字控制模块1产生数字控制信号,第一延时控制模块2接入数字控制信号中的低位数字控制信号,并根据低位数字控制信号对时钟信号进行高精度延时控制;第二延时控制模块3接入数字控制信号中的高位数字控制信号,并根据高位数字控制信号对时钟信号进行低精度延时控制。本实施例中的技术方案,时钟信号首先输入第一延时控制模块2,第一延时控制模块2用于实现高精度的延时控制,然后再通过第二延时控制模块3增加时钟信号整体的延时范围,实现了时钟信号延时控制精度与范围的同时满足,解决了现有技术中接收端的数据以及时钟的相位不完全匹配的问题。并且,本实施例中的技术方案,相较于现有技术中增加时钟数据恢复电路使得接收端的时钟重新锁定数据并恢复数据的技术方案,功耗较低,占用芯片面积较小。

35.可以理解的是,上述各实施例中相同或相似部分可以相互参考,在一些实施例中未详细说明的内容可以参见其他实施例中相同或相似的内容。

36.需要说明的是,在本技术的描述中,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性。此外,在本技术的描述中,除非另有说明,“多个”的含义是指至少两个。

37.流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更多个用于实现特定逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分,并且本技术的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本技术的实施例所属技术领域的技术人员所理解。

38.应当理解,本技术的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。例如,如果用硬件来实现,和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

39.本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

40.此外,在本技术各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。所述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。

41.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

42.尽管上面已经示出和描述了本技术的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本技术的限制,本领域的普通技术人员在本技术的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。