1.本技术涉及半导体领域,更具体地,涉及一种用于开短路检测的半导体结构。

背景技术:

2.在半导体封装技术领域中,现行对于半导体装置的开短路检测(open/short test,ostest)是在半导体组件级别(assembly level)的最终组装步骤之后执行,举例而言,半导体结构中已设置了专用集成电路(asic)控制器和存储器芯片。在现行的检测方式下,如果半导体组件中的一个部件未能通过开短路检测,则会导致整个封装组件被报废,即使该问题是只有涉及芯片接合相关的缺陷,例如,直接芯片贴装(direct die attach,dca) 的接合缺陷,这导致了封装组件制造成本与检测成本的提高。

3.再者,对于采用直接芯片贴装的半导体组件而言,在一些封装设计中,芯片与衬底之间的连接结构存在不与焊接指(bond fingers)相连接,也不会连接到接合垫和球焊垫的凸块连接线路。例如,专用集成电路芯片内部的低压降功率凸点与衬底上的电容器的连接结构。这导致现行对半导体组件级别的开短路检测无法完整的检测直接芯片连接的所有连接线路,且无法检测出部分涉及芯片接合相关的缺陷,从而造成检测效率的低下并导致产品良率检测效果的降低。

4.对此,有必要开发一种新的用于操作系统测试的半导体结构,以改进当前的操作系统测试过程。关于如何优化当前的半导体组件的开短路检测,以避免检测过程中出现无法检测到的连接线路的情况,业内还有很多技术问题需要解决。

技术实现要素:

5.本技术的目的之一在于提供一种半导体结构的检测方法和半导体结构,该检测方法包含对经表面贴装技术(surface molding technology,smt)工艺处理后和/或经直接芯片贴装(dca)工艺处理后的半导体结构进行开短路检测,建立产品良率的防护线,以检测半导体结构中与smt工艺处理/dca工艺处理相关的连接缺陷。本技术通过在smt工艺和dca工艺之后立刻进行的开短路检测可以在半导体封装制备过程的早期阶段检测到与smt工艺处理/dca工艺处理相关的故障,以排除相关缺陷结构,并优化良好半导体结构的后续封装过程。再者,本技术通过减少半导体封装于封装后期阶段才经开短路检测出缺陷,所造成封装材料报废,可以显着节省大量的制备成本。

6.根据本技术的一个方面,本技术提供了一种半导体结构,其包括:衬底,衬底包含第一表面及与第一表面相对的第二表面,其中衬底包括:设置于第一表面上的接合垫,其特征在于,其中半导体结构进一步包含第一检测部件,第一检测部件设置于衬底的第一表面上。

7.在一些实施例中,第一检测部件电连接至接合垫。

8.在一些实施例中,衬底进一步包括设置于衬底的第一表面上的被动部件及第二检测部件,且第二检测部件电连接至被动部件。

9.在一些实施例中,半导体结构进一步包含芯片,芯片设置于衬底的第一表面上,且第二检测部件设置于芯片与被动部件之间。

10.在一些实施例中,芯片设置于第一检测部件与第二检测部件之间。

11.在一些实施例中,芯片包含专用集成电路芯片。

12.在一些实施例中,衬底进一步包含硅穿孔tsv及第三检测部件,第三检测部件设置于衬底的第一表面上,且第三检测部件电连接至硅穿孔。

13.在一些实施例中,第一检测部件、第二检测部件及第三检测部件中的至少一者为检测垫。

14.在一些实施例中,衬底进一步包含球焊垫,球焊垫设置于衬底的第二表面上,且球焊垫电连接至硅穿孔。

15.在一些实施例中,衬底进一步包含连接件,连接件设置于球焊垫上。

16.本技术部分实施例提供的半导体结构中在衬底上设置了一个或多个检测部件,能够通过一个或多个检测部件,在smt工艺/dca工艺处理完成阶段,对半导体结构的连接线路进行开短路测试,以提高开短路测试的检测效率与准确程度。同时,本技术通过将一个或多个检测部件与测试目标的连接结构的连接,例如,连接到asic芯片的无源结构、测试球焊盘和接合垫,能够有效的对半导体结构中芯片与衬底的各式连接结构进行检测,以对半导体结构连接缺陷进行有效的检测。

17.本技术提供的额外层面及优点将部分地在后续说明中描述、显示、或是经由本技术实施例的实施而阐释。

附图说明

18.在下文中将简要地说明为了描述本技术实施例或现有技术所必要的附图以便于描述本技术的实施例。显而易见地,下文描述中的附图仅只是本技术中的部分实施例。对本领域技术人员而言,在不需要创造性劳动的前提下,依然可以根据这些附图中所例示的结构来获得其他实施例的附图。

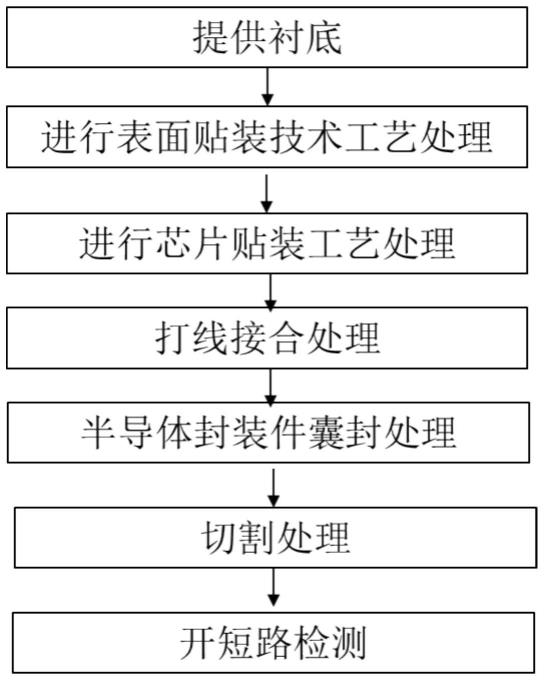

19.图1为根据本技术的一种半导体封装制备方法的流程图。

20.图2为根据本技术部分实施例的一种半导体封装制备方法的流程图。

21.图3为根据本技术部分实施例的一种半导体结构的截面示意图。

22.图4为根据本技术部分实施例的一种半导体结构的截面示意图。

23.图5为根据本技术部分实施例的一种半导体结构的截面示意图。

具体实施方式

24.本技术的实施例将会被详细的描示在下文中。在本技术说明书全文中,将相同或相似的组件以及具有相同或相似的功能的组件通过类似附图标记来表示。在此所描述的有关附图的实施例为说明性质的、图解性质的且用于提供对本技术的基本理解。本技术的实施例不应该被解释为对本技术的限制。

25.如本文中所使用,术语“约”、“大体上”、“实质上”用以描述及说明小的变化。当与事件或情形结合使用时,术语可指代其中事件或情形精确发生的例子以及其中事件或情形极近似地发生的例子。举例来说,当结合数值使用时,术语可指代小于或等于数值的

±

10%

的变化范围,例如小于或等于

±

5%、小于或等于

±

0.5%、或小于或等于

±

0.05%。举例来说,如果两个数值之间的差值小于或等于值的平均值的

±

10%,那么可认为两个数值“大体上”相同。

26.再者,为便于描述,“第一”、“第二”、“第三”、“第四”等等可在本文中用于区分一个图或一系列图的不同组件。除非经特别指定或限定之外,“第一”、“第二”、“第三”、“第四”等等不意欲描述对应组件。

27.在本技术中,除非经特别指定或限定之外,“设置”、“接合”、“连接”以及与其类似的用词在使用上是广泛地,而且本领域技术人员可根据具体的情况以理解上述的用词可是,比如,固定接合、可拆式接合或集成接合;其也可是机械式连接或电连接;其也可是直接连接或通过中介结构的间接连接;也可是两个组件的内部通讯。

28.如图1所示,半导体封装/组件的开短路检测可以是在封装/切割处理后,检测已完成封装的半导体封装/组件的连接线路。当已完成封装的半导体组件的连接线路被检测出存在缺陷时,即便连接缺陷只是由衬底的连接线路或是个别芯片的连接线路的缺陷所导致的,整个半导体封装/组件都将会报废。这导致了半导体封装/组件中所可能包含的一个或多个良好的半导体部件,例如,但不限于,asic芯片、存储器或处理芯片等,将会连同个别芯片的连接线路的缺陷一同报废,进而大幅的提高了半导体封装/组件的制备成本。

29.为了改善前述的半导体封装/组件的开短路检测,本技术另外提供的实施例提供了一种半导体结构的检测方法,如图2所示,该检测方法通过对经表面贴装技术(surfacemolding technology,smt)工艺处理后和/或经直接芯片贴装(dca)工艺处理后的暴露的半导体结构层级(assembly-striped level)进行开短路检测,可以在半导体封装制备过程的早期阶段检测到与smt工艺处理/dca工艺处理相关的故障,从而排除相关缺陷结构所导致的缺陷衬底或芯片,并采用良好的半导体结构进行后续封装过程。该检测方法能够有效的减少封装后期由连接结构缺陷所导致的封装材料及芯片报废,可以显着地节省大量的制备成本。

30.此外,对于采用直接芯片贴装(dca)工艺的半导体结构,其芯片与衬底之间的连接线路中可能存在不与焊接指(bond fingers)相连接,也不会连接到接合垫和球焊垫的凸块连接线路(bump connection)。例如,专用集成电路芯片内部的低压降功率凸点与衬底上的电容器的连接结构。这导致现行对半导体组件级别的开短路检测无法完整的检测直接芯片连接的所有连接线路,且无法检测出部分涉及芯片接合相关的缺陷,从而造成检测效率的低下并导致产品良率检测效果的降低。鉴于上述问题,根据本技术的一个方面,本技术提供了一种半导体结构,该半导体结构通过设置一个或多个检测部件,使一个或多个检测部件分别与半导体结构中的连接线路节点,例如,但不限于,接合垫、被动部件(例如电容和电感等)、球焊垫等,电连接,并通过一个或多个检测部件进行开短路检测,以优化开短路检测的效率与精度。同时,本技术部分实施例通过采用一个或多个检测部件,能够完整的检测半导体结构中的全部连接线路,进而使不同类型的芯片连接设计皆能够适用于开短路检测。

31.如图3所示,在一些实施例中,半导体结构10包括:衬底100及一个或多个检测部件1021、1022、1023,其中衬底100包含第一表面100t及与第一表面100t相对的第二表面100b,且一个或多个检测部件1021、1022、1023设置于衬底100的第一表面 100t上。本技术通过将一个或多个检测部件设置于衬底的第一表面上,能够在单一表面上完成半导体结构的开短

路检测,进而优化开短路检测的操作与检测效率。

32.衬底100的第一表面100t和/或第二表面100b可为实质上平坦的表面。在一些实施例中,衬底100经过切割工艺后能够形成半导体封装的衬底单元。

33.在一些实施例中,衬底100包括设置于第一表面100t的用于与其它任意类型的电子组件电连接的一或多个结合垫101。在一些实施例中,衬底100可包括多个层,层可包括介电层、金属层、及连接单层或多层的电性连通(via)等衬底结构组成。

34.在一些实施例中,检测部件1021电连接至接合垫101,以用于半导体结构10的连接结构的开短路检测。应理解,检测部件与接合垫的连接方式可以是本领域中任何合适的连接方式,而不受其限制。在一些实施例中,检测部件1021包含连接件,该连接件设置于衬底100中,并与接合垫直接连接。

35.在一些实施例中,衬底还包括设置于第一表面100t上的检测部件1022和被动部件 103,且检测部件1022电连接至被动部件103,以用于半导体结构的被动部件103的开短路检测。被动部件103例如,但不限于,电容器和电感器。

36.在一些实施例中,衬底100还包括设置于第一表面100t上的电子元件(未在图中显示)。在一些实施例中,检测部件能够电连接至电子元件,以用于半导体结构的电子元件的开短路检测。应理解,检测部件与电子元件的连接方式可以是本领域中任何合适的连接方式,而不受其限制。

37.如图4所示,在一些实施例中,半导体结构20还包括:芯片201。

38.芯片201设置于衬底100的第一表面100t上。半导体结构中的芯片201可为任意类型的管芯或裸片,例如,但不限于,存储器芯片、处理器芯片、专用集成电路芯片等。在一些实施例中,存储器芯片包含专用集成电路芯片。在一些实施例中,芯片201还包含设置其表面的用于与其它任意类型的电子组件电连接的一或多个连接件202,例如,但不限于,接合凸块(bump)、接合柱(pillar)等。在一些实施例中,芯片201的连接件202与衬底100的第一表面100t的接合垫101形成倒装接合的连接结构。在一些实施例中,检测部件1021能够电连接至芯片201的一或多个连接件202,以用于连接件202与接合垫101所形成的连接结构的开短路检测。

39.应理解,虽然图4所演示的实施例中半导体结构是采用直接芯片贴装工艺所形成的倒装接合(flip-chip bonding)的芯片201与衬底100,然而本技术的检测部件及检测方法可以应用于本领域中任何合适的芯片与衬底的连接结构或接合结构,而不受其限制。在一些实施例中,芯片与衬底的连接为打线连接(wired bonding)。在一些实施例中,芯片与衬底的接合可以是本领域中任何常见的设置方式,例如,但不限于,直接接触接合、粘结剂接合。应理解,芯片的芯片尺寸能够根据芯片设计、封装体尺寸等因素而调整,并不受其限制。

40.在一些实施例中,检测部件1022设置于芯片201与被动部件103之间。

41.在一些实施例中,芯片201设置于检测部件1021与检测部件1022之间,以优化检测线路的分布。

42.在一些实施例中,衬底100进一步包含硅穿孔104及检测部件1023,检测部件1023 设置于衬底的第一表面100t上,且检测部件1023电连接至硅穿孔104。应理解,衬底 100内部可包括根据任何需要所设置的任意形式的连接结构,例如,但不限于,硅穿孔、连接桥等,

而不受其限制。

43.如图4所示,在一些实施例中,衬底100的第二表面上包含阻焊层105及一或多个球焊垫106,其中阻焊层105上存在开口以暴露用于与位于半导体封装外部的其它电子组件电连接的一或多个球焊垫106。在一些实施例中,球焊垫106电连接至硅穿孔104。在一些实施例中,球焊垫106与检测部件1023电连接。

44.如图5所示,在一些实施例中,半导体结构30的衬底100进一步包含连接件107,其中连接件107设置于球焊垫106上。在一些实施例中,连接件107包含,但不限于,接合凸块(bump)、接合柱(pillar)、锡球(solder ball)等。在一些实施例中,连接件107通过球焊垫106、硅穿孔104与检测部件1023电连接。

45.基于本技术上述公开的教示,本领域技术人员可以根据实际需要设计、布置或选择半导体结构中的一个或多个检测部件用于进行开短路检测。在一些实施例中,一个或多个检测部件中的至少一者为检测垫,用于与检测设备之探针接触,以测试电性。

46.本技术的技术内容及技术特点已揭示如上,然而熟悉本领域的技术人员仍可能基于本技术的教示及揭示而作种种不背离本技术精神的替换及修饰。因此,本技术的保护范围应不限于实施例所揭示的内容,而应包括各种不背离本技术的替换及修饰,并为本技术的权利要求书所涵盖。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。